### CCDSC'14 Panel

Exascale topic

Dr. Jean-Laurent PHILIPPE, PhD Technical Sales Director, Western Europe

1-4-1-0----

#### **Legal Information**

- INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL® PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. INTEL PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS.

- Intel may make changes` to specifications and product descriptions at any time, without notice.

- All products, dates, and figures specified are preliminary based on current expectations, and are subject to change without notice.

- Intel, processors, chipsets, and desktop boards may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request.

- Any code names featured are used internally within Intel to identify products that are in development and not yet publicly announced for release. Customers, licensees and other third parties are not authorized by Intel to use code names in advertising, promotion or marketing of any product or services and any such use of Intel's internal code names is at the sole risk of the user.

- Intel, Intel Inside, the Intel Iogo, Centrino, Centrino Inside, Intel Core, Intel Atom and Pentium are trademarks of Intel Corporation in the United States and other countries.

- Material in this presentation is intended as product positioning and not approved end user messaging.

- This document contains information on products in the design phase of development.

- \*Other names and brands may be claimed as the property of others.

- Roadmap not reflective of exact launch granularity and timing please refer to ILU guidance

#### **Problem statement (2011)**

#### **Problem statement (2011)**

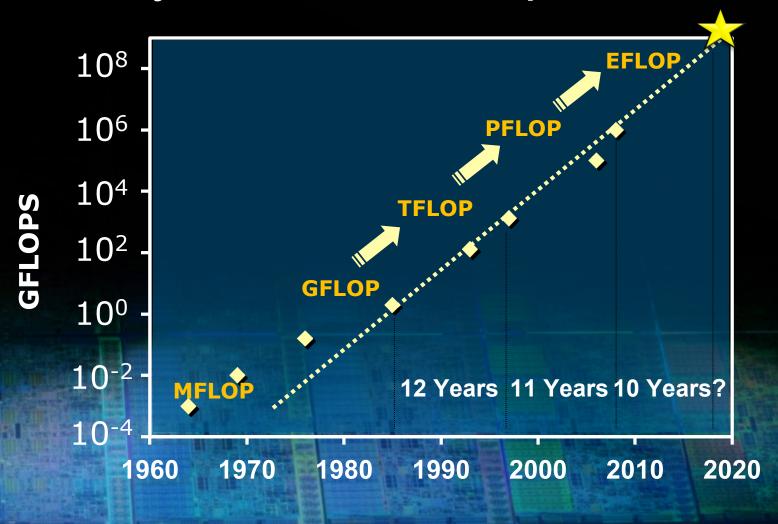

1 EF (ExaFlops) =  $10^{18}$  Flops

How can we achieve this?

It \*could\* take:

- A microarchitecture that does 10 ops/cycle  $10^{1}$

- In a core running at 2GHz

- With 250 cores per socket

- On a 200,000 sockets

2 10<sup>9</sup> 2.5 10<sup>2</sup>

$2 \ 10^5$

1 EF (ExaFlops) =  $10^{18}$  Flops

How can we achieve this?

It \*could\* take:

| _   |                      |               |           | 1 A 1    |

|-----|----------------------|---------------|-----------|----------|

| - Δ | microarchitecture    | that does 10  | ons/cycle | $10^{1}$ |

|     | Thich but childeduic | tilat does to | ops/cycic |          |

- In a core running at 2GHz

- With 100 cores per socket

- On a 500,000 sockets

$2.10^9$   $10^2$

$5.10^{5}$

1 EF (ExaFlops) =  $10^{18}$  Flops

How can we achieve this?

It \*could\* take:

| - Δ | microar  | chitecture  | that does  | 10 o | ns/cycle  | $\sim 10^{1}$ |

|-----|----------|-------------|------------|------|-----------|---------------|

|     | IIICIUai | Cilitecture | triat does | TO O | ps/ cycle |               |

- In a core running at 1GHz

- With 500 cores per socket

- On a 200,000 sockets

2 10<sup>5</sup>

10<sup>9</sup>

$5 10^2$

1 EF (ExaFlops) =  $10^{18}$  Flops

How can we achieve this?

It \*could\* take:

| - A microarchitecture that does 10 ops/cycle | TO-             |

|----------------------------------------------|-----------------|

| - In a core running at 1GHz                  | 10 <sup>9</sup> |

| - With 1,000 cores per socket                | 10 <sup>3</sup> |

$10^5$

- On a 100,000 sockets

# Today's Exascale Expectation

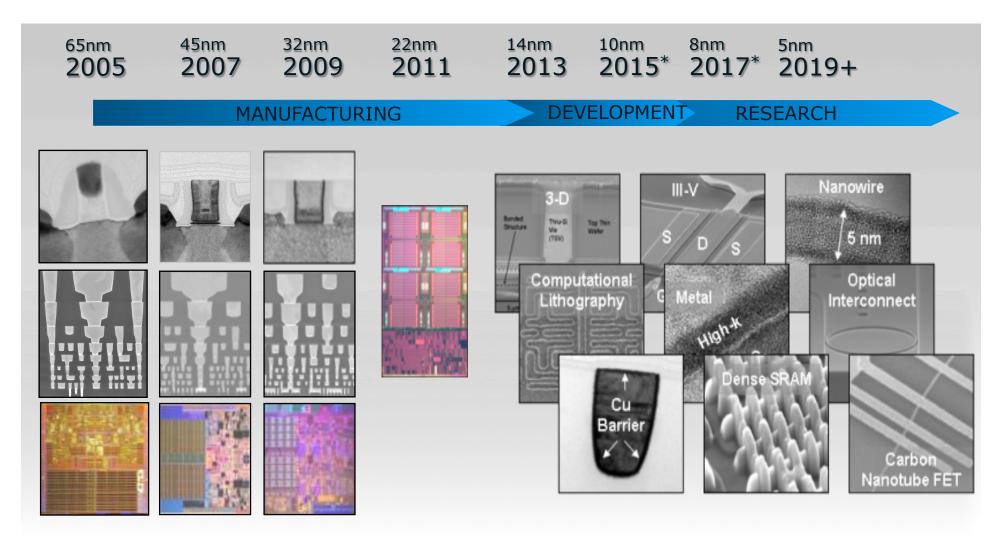

#### **Moore's Law**

<sup>\*</sup> All products, dates, and figures specified are preliminary based on current expectations, and are subject to change without notice.

#### Moore's Law - 22nm Tri-Gate

3<sup>rd</sup> Generation Intel® Core™ Processor **Family** (2012, codename

IvyBridge)

VS.

4004 (1971)

4,000X Faster

5,000X Less Energy / Transistor

50,000X Cheaper / Transistor

Source: Intel