#### **DARPA's HPCS Program: History, Models, Tools, Languages**

Jack Dongarra, University of Tennessee and Oak Ridge National Lab **Robert Graybill, USC Information Sciences Institute** William Harrod, DARPA **Robert Lucas. USC Information Sciences Institute Ewing Lusk, Argonne National Laboratory** Piotr Luszczek, University of Tennessee Janice McMahon, USC Information Sciences Institute Allan Snavely, University of California – San Diego Jeffery Vetter, Oak Ridge National Laboratory Katherine Yelick, Lawrence Berkeley National Laboratory Sadaf Alam, Oak Ridge National Laboratory **Roy Campbell, Army Research Laboratory** Laura Carrington, University of California - San Diego Tzu-Yi Chen, Pomona College **Omid Khalili, University of California – San Diego** Jeremy Meredith, Oak Ridge National Laboratory Mustafa Tikir, University of California - San Diego

#### Abstract

The historical context surrounding the birth of the DARPA High Productivity Computing Systems (HPCS) program is important for understanding why federal government agencies launched this new, longterm high performance computing program and renewed their commitment to leadership computing in support of national security, large science, and space requirements at the start of the 21<sup>st</sup> century. In this chapter we provide an overview of the context for this work as well as various procedures being undertaken for evaluating the effectiveness of this activity including such topics as modeling the proposed performance of the new machines, evaluating the proposed architectures, understanding the languages used to program these machines as well as understanding programmer productivity issues in order to better prepare for the introduction of these machines in the 2011-2015 timeframe.

| DARPA's HPCS Program: History, Models, Tools, Languages |      |

|---------------------------------------------------------|------|

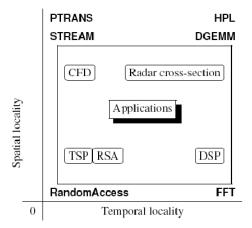

| 1.1 HPCS Motivation                                     | 9    |

| 1.2 HPCS Vision                                         | . 11 |

| 1.3 Program Overview                                    | . 13 |

| 1.4 Cray "Cascade" and IBM "PERCS" Overview             | . 15 |

| 2. Productivity Systems Modeling                        |      |

| 2.1 Problem Definition and Unified Framework            | . 20 |

| 2.2 Methods to Solve the Convolution Problem            | . 22 |

| 2.2.1 Empirical Method                                  | . 22 |

| 2.2.2 Solving for A using Least Squares                 | . 23 |

| 2.2.3 Solving for A using Linear Programing             |      |

| 2.2.4 Ab Initio Method                                  |      |

| 2.2.5 Experimental Results                              |      |

| 2.2.6 Fitting the data using Least Squares              |      |

| 2.2.7 Detecting Outliers By Using Linear Programming    |      |

| 2.3 Performance prediction                              |      |

| 2.3.1 Empirical methods                                 |      |

| 2.3.2 Ab initio methods                                 |      |

| 2.4 Related Work                                        |      |

| 2.5 Conclusions                                         |      |

| 3. Productivity Evaluation on Emerging Architectures    |      |

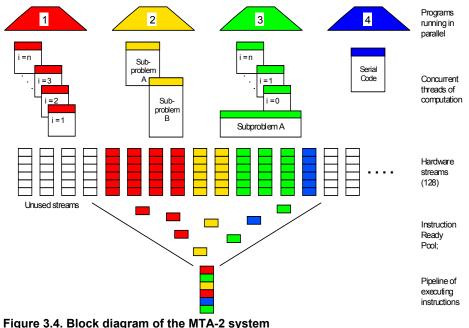

| 3.1 Architecture Overviews                              |      |

| 3.1.1 Homogeneous Multi-core Processors                 |      |

| 3.1.2 Cell Broadband Engine                             |      |

| 3.1.3 Graphics Processing Units                         |      |

| 3.1.4 Cray MTA-2                                        |      |

| 3.2 Target Workloads                                    |      |

| 3.2.1 Hyperspectral Imaging (HSI)                       |      |

| 3.2.2 Molecular Dynamics                                |      |

| 3.3 Evaluation                                          |      |

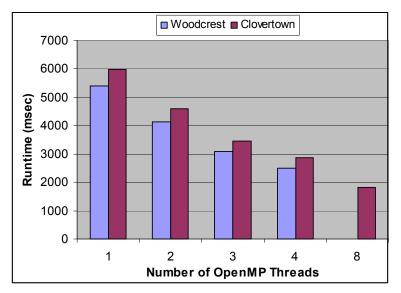

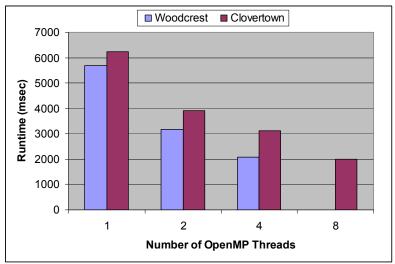

| 3.3.1 Homogeneous Multi-core Systems                    |      |

| 3.3.2 Cell Broadband Engine                             |      |

| 3.3.3 GPU                                               |      |

| 3.3.4 MTA-II                                            |      |

| 3.4 Productivity                                        |      |

| 4. The DARPA HPCS Language Project                      |      |

| 4.1 Architectural Developments                          | . 53 |

| 4.2 The HPCS Languages as a Group                       |      |

| 5. Research on Defining and Measuring Productivity      |      |

| 5.1 Software Development Time                           |      |

| 5.1.1 Understanding the Users                           |      |

| 5.1.2 Focusing the Inquiry                              |      |

| 5.1.3 Developing the Evaluation Tools                   |      |

| 5.1.4 Advanced Tools for Engineers                      |      |

| 5.2 Productivity Metric                                 | , 74 |

| 5.2.1 Business Perspective                        | 75 |

|---------------------------------------------------|----|

| 5.2.2 System Perspective                          |    |

| 5.3 Conclusions                                   | 77 |

| 6. The HPC Challenge Benchmark Suite              | 78 |

| 6.1 The TOP500 Influence                          | 80 |

| 6.2 Short History of the Benchmark                | 80 |

| 6.2.1 The Benchmark Tests' Details                | 81 |

| 6.2.2 Benchmark Submission Procedures and Results | 82 |

| 6.2.3 Scalability Considerations                  | 84 |

| 6.3 Conclusions                                   | 85 |

| 7. Summary: The DARPA HPCS Program                | 86 |

| References                                        | 87 |

#### 1. HISTORICAL BACKGROUND

The historical context surrounding the birth of the High Productivity Computing Systems (HPCS) program is important for understanding why federal government agencies launched this new, long-term high performance computing program and renewed their commitment to leadership computing in support of national security, large science, and space requirements at the start of the 21<sup>st</sup> century.

The lead agency for this important endeavor, not surprisingly, was DARPA, the Defense Advance Research Projects Agency. DARPA's original mission was to prevent technological surprises like the launch of Sputnik, which in 1957 signaled that the Soviets had beaten the U.S. into space. DARPA's mission is still to prevent technological surprises, but over the years it has expanded to include creating technological surprises for America's adversaries. DARPA conducts its mission by sponsoring revolutionary, high-payoff research that bridges the gap between fundamental discoveries and their military use. DARPA is the federal government's designated "technological engine" for transformation, supplying advanced capabilities, based on revolutionary technological options.

Back in the 1980s, a number of agencies made major investments in developing and using supercomputers. The High Performance Computing and Communications Initiative (HPCCI), conceived in that decade, built on these agency activities and in the 1990s evolved into a broad, loosely coupled program of computer science research. Key investments under the HPCCI and other programs have enabled major advances in computing technology and helped maintain U.S. leadership in the world computer market in recent decades.

In the late 1990s and early 2000s, U.S. government and industry leaders realized that the trends in high performance computing were creating technology gaps. If left unchecked, these trends would threaten continued U.S superiority for important national security applications and could also erode the nation's industrial competitiveness. The most alarming trend was the rapid growth of less-innovative, commodity-based clustered

computing systems ("clusters"), often at the expense of the leading-edge, capability class of supercomputers with key characteristics supportive of an important set of applications. As a result of this strong market trend, the entire ecosystem needed to maintain leadership in high-end, capability-class supercomputers was in peril: the few companies producing high-end supercomputers had less money to invest in innovative hardware research and development, and firms that created high-performance versions of software applications, environments, and tools for high-end supercomputers had a more difficult time making a business case for this specialized activity. The seemingly inexorable advance of commodity microprocessor speeds in obedience to Moore's Law propelled the growth of clusters with hundreds, then thousands of processors (although this same increasing parallelism also gave rise to the programming challenge that continues to plague the high performance computing industry today).

#### A CHRONOLOGY

The goal of this section is to provide the first comprehensive chronology of events related to the HPCS program. The chronology is based on reports, documents and summaries that have been accumulated over time by more people than I can mention here. Special credit is due to Charles Holland, Richard Games and John Grosh for their contributions, especially in the early years leading up to the HPCS program. In the chronology, events that were part of the HPCS program, or sponsored by the program, are highlighted in italics.

**1992:** DARPA funding support focuses on companies developing massively parallel processing (MPP) systems based on commodity microprocessors (e.g., Thinking Machines' Connection Machine CM5, Intel's Paragon system).

**1995**: The Department of Energy establishes the Accelerated Strategic Computing Initiative (ASCI) to ensure the safety and reliability of the nation's nuclear weapons stockpile through the use of computer simulation rather than nuclear testing. ASCI adopts commodity HPC strategy.

**25 February 1996:** Silicon Graphics acquires Cray Research, which becomes a subsidiary of SGI.

**17 May 1996**: The University Corporation for Atmospheric Research (UCAR), a federally funded agency in Boulder, Colorado, awards a \$35 million contract for a supercomputer purchase to a subsidiary of NEC of Japan. The U.S.-based subsidiary of NEC outbids two other finalists for the contract—Fujitsu U.S. and Cray Research of Eagan, Minnesota—to supply a supercomputer to UCAR's National Center for Atmospheric Research (NCAR) for modeling weather patterns.

**29 July 29 1996**: Cray (now an SGI subsidiary) petitions the International Trade Administration (ITA), a division of the U.S. Commerce Department, claiming that it had

been the victim of "dumping." The ITA upholds the dumping charge and the NCAR purchase of the NEC supercomputer is cancelled.

**19 June 1997**: Sandia National Laboratories' "ASCI Red" massively parallel processing system uses 9,216 Intel Pentium Pro microprocessors to achieve 1.1 trillion floating point operations per second on the Linpack benchmark test, making it the top supercomputer in the world and the first to break the teraflop/s barrier.

**26 September 1997**: The International Trade Commission (ITC) determines that Cray Research has suffered "material injury" and imposes punitive tariffs of between 173% and 454% on all supercomputers imported from Japan, a barrier so high it effectively bars them from the U.S. market.

**22 September 1999**: SGI announces that it will be receiving significant financial aid from several U.S. government agencies, including the National Security Agency (NSA), to support the development of the company's Cray SV2 vector supercomputer system.

**15 November 1999**: Jacques S. Gansler tasks the Defense Science Board (DSB) to address DoD supercomputing needs, especially in the field of cryptanalysis.

**2 March 2000**: Tera Computer Company acquires the Cray vector supercomputer business unit and the Cray brand name from SGI. Tera renames itself as Cray Inc.

**11 October 2000**: The DSB Task Force on DoD Supercomputing Needs publishes its report. The Task Force concludes current commodity-based HPCs are not meeting the computing requirements of the cryptanalysis mission. The Task Force recommends that the government:

- (1) Continue to support the development of the Cray SV2 in the short term.

- (2) In the midterm, develop an integrated system that combines commodity

- microprocessors with a new, high-bandwidth memory system.

- (3) Invest in research on critical technologies for the long term.

*Fall 2000:* DARPA Information Technology Office (ITO) sponsors high performance computing technology workshops led by Candy Culhane and Robert Graybill (ITO)

**23 March 2001**: Dave Oliver and Linton Wells, both from the DoD, request a survey and analysis of national security high performance computing requirements to respond to concerns raised by U.S. Representative Martin Sabo (D-Minn.) that eliminating the tariffs on Japanese vector supercomputers would be a bad idea.

**April 2001**: Survey of DoD HPC requirements concludes that cryptanalysis computing requirements are not being met by commodity-based high performance computers, although some DoD applications are being run reasonably well on commodity systems because of a significant investment by the DoD HPC Modernization Program to make their software compatible with the new breed of clusters. But the survey also reveals

significant productivity issues with commodity clusters in almost all cases. The issues range from reduced scientific output due to complicated programming environments, to inordinately long run times for challenge applications.

**26 April 2001**: Results of the DoD HPC requirements survey are reviewed with Congressman Sabo. Dave Oliver, Delores Etter, John Landon, Charlie Holland, and George Cotter attend from the DoD. The DoD commits to increasing its R&D funding to provide more diversity and increase the usefulness of high performance computers for their applications.

3 May 2001: Commerce Department lifts tariffs on vector supercomputers from Japan

11 June 2001: Release of the DoD Research and Development Agenda for High Productivity Computing Systems White Paper, prepared for Dave Oliver and Charlie Holland. The white paper team was led by John Grosh (Office of the Deputy Under Secretary of Defense for Science and Technology) and included Robert Graybill (DARPA)), Dr. Bill Carlson (Institute for Defense Analysis Center for Computing Sciences), and Candace Culhane. The review team consisted of Dr. Frank Mello (DoD High Performance Computing Modernization Office), Dr. Richard Games (The MITRE Corporation), Dr. Roman Kaluzniacki, Mr. Mark Norton (Office of the Assistant Secretary of Defense, Command, Control, Communications, and Intelligence), and Dr. Gary Hughes.

*June 2001:* DARPA ITO sponsors an IDA Information Science and Technology (ISAT) summer study, "The Last Classical Computer," chaired by Dr. William J. Dally from Stanford University.

July 2001: DARPA approves High Productivity Computing Systems Program based to large degree on the HPCS white paper and ISAT studies. Robert Graybill is the DARPA program manger. The major goal is to provide economically viable high productivity computing systems by the end of 2010. These innovative systems will address the inherent difficulties associated with the development and use of current high-end systems and applications, especially programmability, performance, portability and robustness.

To achieve this aggressive goal, three program phases are envisioned: (1) concept study; (2) research and development; and (3) design and development of a petascale prototype system. The program schedule is defined as follows:

- *I.* June 2002 June 2003: Five vendors to develop concept studies for an HPC system to appear in 2010.

- II. July 2003 June 2006: Expected down selection to 2 3 vendors (number depends on funding level) to develop detailed system designs for the 2010 system and to perform risk reduction demonstrations.

- *III.* July 2006 December 2010: Down selection to 1 2 vendors (number depends on funding level) to develop research prototypes and pilot systems.

*January 2002:* DARPA's HPCS Phase I Broad Area Announcement (BAA) is released to industry.

**February 2002**: Congress directs the DoD to conduct a study and deliver by 1 July 2002 a development and acquisition plan, including budgetary requirements for a comprehensive, long-range Integrated High-End Computing (IHEC) program. NSA is designated as the lead agency. DARPA, the DoD HPC Modernization Program, NIMA, NRO, DOE/NNSA, and NASA are named as contributing organizations.

**8 March 2002**: NEC Corporation announces the delivery of its vector parallel computing system based on the NEC SX-6 architecture to the Japanese Earth Simulator Center. The system sustains 35.6 Tflop/s on the Linpack benchmark, making it the fastest computer in the world—approximately 5 times faster than the previous #1, the DOE "ASCI White" computer at the Lawrence Livermore National Laboratory. Jack Dongarra, who helps compile the Top500 computer list, compares the event's shock impact with the Sputnik launch, and dubs it "Computenik."

**May-June 2002**: The NSA-led Integrated High-End Computing (IHEC) study commences with a number of focused workshops.

June 2002: Phase I of the DARPA HPCS program begins with one-year study contracts awarded to Cray, HP, IBM, SGI, and Sun. NSA provides additional funds for Phase I awards. The goal of the program is to develop a **new revolutionary generation** of **economically viable** high productivity computing systems for national security and industrial user communities by 2010, in order to **ensure U.S. leadership, dominance, and control** in this critical technology

The vendors' conceptualizing efforts include a high degree of university participation (23), resulting in a wealth of novel concepts. In addition, a number of innovative technologies from DARPA's active embedded programs are considered by the vendors: Data Intensive Systems (DIS), Polymorphous Computing Architectures (PCA), and Power Aware Computing and Communications (PACC).

**21 October 2002**: Sandia National Laboratories and Cray Inc. announce that they have finalized a multiyear contract, valued at approximately \$90 million, under which Cray will collaborate with Sandia to develop and deliver a new supercomputer called Red Storm. The machine will use over 16,000 AMD Opteron microprocessors and have a peak processing rate of 100 trillion floating point operations per second.

**21 November 2002**: Users of the Japanese Earth Simulator capture three out of five Gordon Bell prizes awarded at the Supercomputing 2002 conference. In one case, scientists run a 26.58 Tflop/s simulation of a complex climate system. This corresponds to 66% of the peak processing rate. Competing commodity systems in the U.S. deliver 10% or less of peak rates, illustrating one of the productivity issues that the DARPA HPCS program is proposing to address.

**Dec 2002**: The FY03 federal budget includes language proposing the development of an interagency R&D roadmap for high-end computing core technologies, along with a federal high-end computing capacity and accessibility improvement plan. In response to this guidance, the White House Office of Science and Technology Policy (OSTP), in coordination with the National Science and Technology Council, commissions the creation of the interagency High-End Computing Revitalization Task Force (HECRTF). The interagency HECRTF is charged with developing a five-year plan to guide future federal investments in high-end computing.

**June 2003:** Computing Research Association leads a workshop, chaired by Dr. Daniel A. Reed, on "The Road for the Revitalization of High-End Computing," as part of the High-End Computing Revitalization Task Force's effort to solicit public comment on the planning process.

July 2003: DARPA HPCS Phase I down-select is completed and Phase II three-year research and development Other Transactions Authority (OTA) contracts are awarded to Cray, IBM, and Sun.

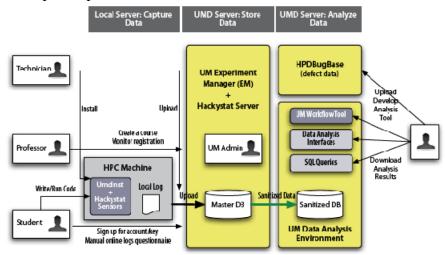

July 2003: A multi-agency initiative (DARPA, DOE Office of Science, NNSA, NSA, NSF, and NASA) funds a three-year HPCS productivity team effort led by Dr. Jeremy Kepner from MIT-Lincoln Laboratory. The productivity team is comprised of universities, laboratories, Federally Funded Research and Development Centers (FFRDCs) and HPCS Phase II vendors. Bi-annual public productivity conferences are held on a regular basis throughout the three-year Phase II program.

**10 May 2004**: High-End Computing Revitalization Task Force (HPCRTF) Report is released by the Office of the Science and Technology policy (OSTP)

*May 2004*: DARPA sponsors the High Productivity Language System (HPLS) workshop, which is organized by Dr. Hans P. Zima from JPL to form the basis for the HPCS experimental language development activity. Experimental languages discussed include Chapel (Cray), X10 (IBM), and Fortress (Sun).

*Nov 2004*: First formal public announcement is made at the Supercomputing Conference (SC2004) of the new HPC Challenge benchmarks, based on the work done under the HPCS Productivity Team efforts led by the University of Tennessee.

**2004:** The National Research Council (NRC) releases a report, "The Future of Supercomputing," sponsored by the DOE Office of Science.

**August 2005**: Completion of the report from the Joint UK Defense Scientific Advisory Council and U.S. Defense Science Board Study on Critical Technologies. High Performance Computing is identified as a critical technology and the report makes key recommendations to maintain U.S. /UK HPC superiority. Sept 2005: The Army High Performance Computing Research Center (AHPCRC) and DARPA sponsor the first Parallel Global Address Space (PGAS) programming models conference in Minneapolis. Based on the interest level in the first conference, the plan is to turn this event into an annual conference.

*Nov 2005*: First HPC Challenge performance and productivity awards are made at *SC2005*.

*Dec 2005:* Dr. William Harrod becomes the HPCS program manager after Robert Graybill's six year DARPA term expires.

*Nov 2006*: DARPA HPCS Phase II down-select is completed. Phase III multi-year prototype development Other Transaction Authority (OTA) cost-sharing contracts are awarded to Cray and IBM, with petascale prototype demonstrations planned for the end of 2010. This is a mulit-agency effort involving DARPA (lead agency), NSA, DOE Office of Science, and NNSA (the HPCS mission partners) each contributing to Phase III funding.

As this chronology suggests, this period represented a tumultuous transition period for supercomputing, resulting in no shortage of reports, recommendations, and ideas on the roles of public and private sector in maintaining U.S. superiority from the national security and economic perspectives. There was also growing public awareness that theoretical ("peak") performance could no longer be a sufficient measure of computing leadership. During this period of public/private partnerships, the future of supercomputing has been altered by new wave of innovations and real sense that the real value of the computing is in achieving end users business objectives, agency mission and scientific discovery.

#### 1.1 HPCS Motivation

As already noted, high performance computing was at a critical juncture in the United States in the early 2000s, and the HPCS program was created by DARPA in partnership with other key government agencies to address HPC technology and application challenges for the next decade.

A number of DoD studies<sup>1, 2</sup> stressed that there is a national security *requirement* for high performance computing systems, and that, consistent with this requirement, DoD historically had provided partial funding support to assist companies with R&D for HPC systems. Without this government R&D participation, high-end computing might one day

<sup>&</sup>lt;sup>1</sup> "Task Force on DOD Supercomputing Needs," Defense Science Board Study, October 11, 2000.

<sup>&</sup>lt;sup>2</sup> "Survey and Analysis of the National Security High Performance Computing Architectural Requirements," Presentation by Dr. Richard Games, MITRE, April 26, 2001.

<sup>&</sup>lt;sup>3</sup> "DARPA HPCS Application Analysis and Productivity Assessment," MITRE, October 6, 2002.

be available only through manufacturers of commodity clusters based on technologies developed primarily for mass-market consumer and business needs.

While driving U.S. superiority in high-end computing technology, the HPCS program will also contribute significantly to leadership in these and other critical DoD and industrial applications areas: operational weather and ocean forecasting; planning for the potential dispersion of airborne contaminants; cryptanalysis; weapons (warheads and penetrators); survivability/stealth design; intelligence/surveillance/reconnaissance systems; virtual manufacturing/failure analysis of large aircraft, ships, and structures; and emerging biotechnology applications. The HPCS program will create new systems and software tools that will lead to increased productivity of the applications used to solve these critical problems.

The critical mission areas are described below. Some descriptions were derived from a report submitted to Congress by the Office of the Secretary of Defense ("High Performance Computing for the National Security Community") Others came from a report created by MITRE<sup>3</sup>. The list is not exhaustive. HPCS systems are likely to be used for other missions—both military and commercial—if the systems provide a balanced architecture and are easy to use.

<u>Operational Weather and Ocean Forecasting</u> – Provides worldwide 24-hour weather guidance to the military, CIA, and Presidential Support Unit for current operations, weapons of mass destruction contingency planning, etc.

<u>Signals Intelligence</u> – The transformation, cryptanalysis, and intelligence analysis of foreign communications on the intentions and actions of foreign governments, militaries, espionage, sabotage, assassinations, or international terrorism. There are both research and development and operational aspects of this activity.

<u>Intelligence</u>, surveillance, and reconnaissance – Processing the outputs of various types of sensors to produce battlespace situation awareness or other actionable intelligence. Includes target cueing, aided target recognition, and other special exploitation products. These operational applications have to meet throughput and latency requirements as part of a larger system.

<u>Dispersion of airborne contaminants</u> – Predicts the dispersion of hazardous aerosols and gasses in the atmosphere. Supports military operation planning and execution, intelligence gathering, counter terrorism, and treaty monitoring.

<u>Weapons design</u> – Uses computer models to augment physical experimentation to reduce costs and explore new concepts that would be difficult to test. Computational mechanics are used to understand complex projectile-target interactions to develop advanced survivability and lethality technologies. Computational fluid dynamics is used for modeling flight dynamics of missiles and projectiles.

<u>Survivability and stealth</u> – Includes performing research into reducing the radar signatures of airplanes such as the JSF and F22, and providing technical support for acquisition activity. Uses computational electromagnetics for radar cross-section/signature prediction.

<u>Engineering design of large aircraft, ship and structures</u> – Applies computational structural mechanics used to do forensic analysis after terrorist bomb attacks and predictive analysis for the design of safer military and embassy structures. Augments aircraft wind tunnel experiments to reduce costs.

<u>Biotechnology</u> – Uses information technology to create, organize, analyze, store, retrieve and share genomic, proteomic, chemical and clinical data in the life sciences. This area is not strictly considered a national security mission area, but it is of use to the military. More important, it is a growing field in private industry. If HPCS meets biotechnology users' needs, it may enhance the commercial viability of computer systems developed under the HPCS program.

#### 1.2 HPCS Vision

The HPCS vision of developing economically viable high productivity computing systems, as originally defined in the HPCS white paper, has been maintained throughout the life of the program. The vision of economically viable—yet revolutionary—petascale high productivity computing systems led to significant industry and university partnerships early in the program and a heavy industry focus later in the program. To achieve the HPCS vision, DARPA created a three phase program. A broad spectrum of innovative technologies and concepts were developed during Phase I. These were then evaluated and integrated into a balanced, innovative preliminary system design solution during Phase II. Now, in Phase III, the systems are under development, with prototype petascale demonstrations planned for late 2010.

The end product of the HPCS program will be systems with the ability to efficiently run a broad spectrum of applications and programming models in support of the national security and industrial user communities. HPCS is focusing on revolutionary, productivity-enhancing improvements in the following areas:

- **Performance:** Computational capability of critical national security applications improved by 10X to 40X over the 2002 capability.

- **Programmability:** Reduce time to develop, operate, and maintain HPCS application solutions to one-tenth of 2002's cost.

- **Portability:** Make available research and operational HPCS application software that is independent of specific hardware and software architectures.

- **Robustness (Reliability):** Continue operating in the presence of localized hardware failure, contain the impact of software defects, and minimize the likelihood of operator error.

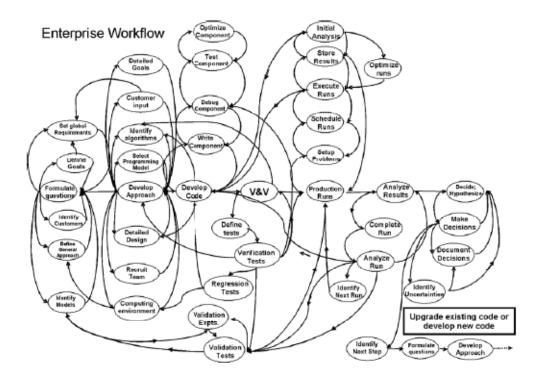

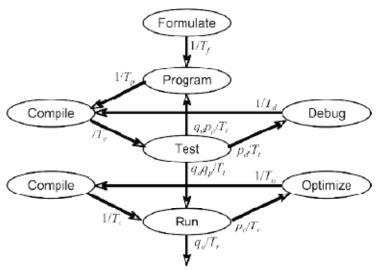

Achieving the HPCS vision will require an optimum balance between revolutionary system requirements incorporating high risk technology, and features and functionality needed for a commercial viable computing system. The HPCS strategy has been to encourage the vendors to not simply develop evolutionary systems, but to make bold step *productivity* improvements, with the government helping to reduce the risks through R&D cost sharing. Productivity, by its very nature, is difficult to assess because it depends upon the specifics of the end user mission, applications, team composition, and end use or workflow as shown in Figure 1.1. A proper assessment requires a mixture of qualitative and quantitative (preferred) analysis to develop a coherent and convincing argument. The productivity goals of the HPCS Phase III system can be loosely grouped into **execution time and development time** goals. The goals of the program have been refined over the three phases as they have gone through this very challenging balancing process. The following refined goals have emerged from that process.

#### Productivity (development time) goals.

- Improve development productivity by 10X over 2002 development productivity for specified government workflows (Workflows 1, 2, 4 and 5).

- Improve execution productivity to 2 petaflops sustained performance (scalable to greater than 4 petaflops) for Workflow 3.

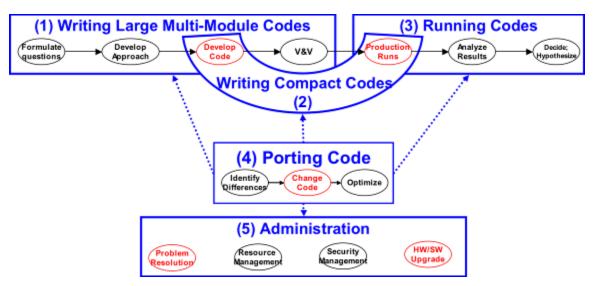

**Figure 1.1. Level 1 Functional Workflows.** Workflows comprise several steps; many overlapping. Items in red represent areas with highest HPC-specific interest.

No single productivity number applies to workflows for the 2002 starting point, or to 2010 workflows. Productivity will vary based on the specific machine, user, and application. DoD and other government agencies will determine 2002 baseline productivity metrics for their government applications and mission requirements, and will then evaluate the petascale prototype system to demonstrate the 10X improvement.

The HPCS program must address overarching issues impeding the development and

utilization of high-end computational systems:

- Balanced system performance

- Improved software tools and methodologies

- Robustness strategy

- Performance measurement and prediction

- System tailorability (ability to scale up and out)

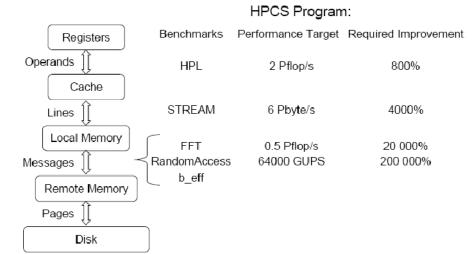

The following Table 1.1 lists the current and HPCS-targeted capabilities (execution time) for HPC systems. Note that "current" is defined as 2007, rather than the program's 2002 starting point.

| Benchmark                                                | Description                                         | Current | HPCS |

|----------------------------------------------------------|-----------------------------------------------------|---------|------|

| Global High-<br>Performance LINPACK<br>(G-HPL)<br>(PF/s) | Sustained execution speed @ local nodes             | ~0.2    | 2+   |

| STREAM<br>(PB/s)                                         | Data Streaming mode – data processing rate          | ~0.1    | 6.5  |

| Global Random Access<br>(GUPS/s)                         | GUPS – Random Access across entire memory system    | 35      | 64K  |

| Bisection B/W<br>(PB/s)                                  | Min bandwidth connecting equal halves of the system | ~.00101 | 3.2  |

# Table 1.1. Performance (Execution times) derived from HPC Challenge Benchmarks

These future HPC systems will also have to operate as major subsystems of the HPCS mission partners' computing centers and meet their growing input/output and data storage requirements. The goals listed below represents the mission partners' requirements.

- 1 trillion files in a single file system

- 10,000 metadata operations per second

- Streaming I/O at 30 GB/sec full duplex

- Support for 30,000 nodes

These objectives cannot be met simply by tracking Moore's Law and leveraging evolutionary commercial developments, but will require revolutionary technologies and close partnerships between vendors and candidate procurement agencies. A fall back to evolutionary HPC systems with a focus on performance at the expense of productivity by vendor product organizations is not an acceptable alternative.

#### 1.3 Program Overview

The HPCS acquisition strategy shown in Figure 2.1 is designed to enable and encourage revolutionary innovation by the selected contractor(s) in close coordination with government HPC end users.

#### **DARPA HPCS** Program Phases I - III

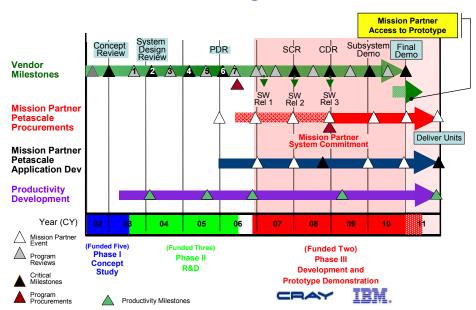

Figure 1.2, HPCS Program and Acquisition Strategy

As Figure 1.2 illustrates, the DARPA-led HPCS program (denoted by the arrow labeled "Vendor Milestones") is divided into three phases. Phase I, an industry concept study, was completed in 2003. DARPA awarded 12-month contracts to industry teams led by Cray, HP, IBM, SGI, and Sun. The study provided critical technology assessments, revolutionary HPCS concept solutions, and new productivity metrics in order to develop a new class of high-end computers by the end of this decade. The outputs from Phase I convinced government decision-makers of the merits of continuing the program.

Phase II was a three-year effort that began with continuation awards to the Cray, IBM and Sun teams. These teams performed focused research, development, and risk reduction engineering activities. The technical challenges and promising solutions identified during the Phase I concept study were explored, developed, and simulated or prototyped. The work culminated in the contractors' preliminary HPCS designs. These designs, along with the vendors' risk reduction demonstrations, analyses, lifecycle cost projections, and their Phase III proposals were used by the decision-makers to determine whether it was technically feasible and fiscally prudent to continue to develop and procure HPCS systems.

Phase III, now under way, is a design, development and prototype demonstration effort that will last four and a half years. The Phase III vendors, Cray and IBM, will complete the detailed design and development of a productive, petascale system and will prove out the system by demonstrating a petascale prototype. They will demonstrate the HPCS performance and productivity goals for an agreed-upon set of applications by the end of 2010. The Phase III mission partners will have access to these systems for the first six months in 2011. Figure 1.2, in addition, outlines the relationship between the HPCS program and agency procurement programs aimed at addressing the petascale computing challenges of the DOE Office of Science, National Nuclear Security Agency, National Security Agency, and the National Science Foundation.

#### 1.4 Cray "Cascade" and IBM "PERCS" Overview

Cray and IBM have provided summaries of their proposed Phase III systems with special emphasis on their revolutionary hardware and software architectures resulting in significant improvement in overall user productivity. Detailed descriptions of the Phase III vendors' innovative architectures are not described here, due to the proprietary nature of the designs at this time. The authors encourage readers to inquire directly with Cray and IBM for fuller descriptions of their novel system architectures.

#### The Cray Cascade System

Cray's Cascade system is based on two observations regarding high performance computing and productivity. The first is that no one processing technology is best for all applications. Application requirements and coding paradigms vary widely, and different forms of parallelism can be best exploited by different processor architectures. Effort spent trying to fit code onto a particular processing architecture is one the largest drains on productivity. The second observation is that programming productivity starts with appropriate support at the architectural level. Machine characteristics such as the compute/bandwidth balance, overhead of synchronization, availability of threads and latency tolerance of processors have a significant impact on software's ability to efficiently exploit a variety of code constructs and allow programmers to express problems in the most natural way.

The Cascade system is designed to be highly configurable and extensible. It provides a high-bandwidth, globally addressable memory, and supports multiple types of compute blades that can be tailored for different application requirements. The interconnect can be dialed from low to very high local and global bandwidth, and scales to well over 100,000 compute nodes with low network diameter. Compute blades in Cascade use commodity microprocessors augmented with both communication and computational accelerators. The communication accelerators extend the address space, address translation and communication and efficient message-passing support. The computational accelerators, based on massively multithreaded and vector technology, can adapt their mode of operation to the characteristics of the code, and provide significant speedup with little programmer intervention. Typical parallel architectures present numerous barriers to achieving high performance, largely related to memory access, and communication and synchronization between threads. The Cascade architecture removes many of these

barriers, allowing programmers to write codes in a straightforward, intuitive manner and still achieve high performance. The key attributes of the architecture are motivated by a desire to both increase performance and improve programmability:

- Cascade provides a large, globally addressable memory and extremely high global bandwidth. This enables very low-overhead access to shared data, which allows programmers to express algorithms naturally, rather than laboring to reduce and lump together inter-processor communication.

- To better serve a variety of application requirements and to support more natural parallel programming idioms, the system provides a set of heterogeneous processing capabilities, each optimized for executing a different style of computation. Serial and latency sensitive computations are executed on commodity microprocessors, data-parallel computations with regular control flows are accelerated by vector processing, and parallel computations with irregular control flows are accelerated via massive multithreading.

- The system supports low overhead, heavily-pipelined communication and synchronization, allowing fine-grained parallelization and enhancing scalability.

The processor and system architecture support a programming environment that greatly simplifies the parallel programming task via higher productivity languages and programming models, and innovative tools that ease debugging and performance tuning at large scales. The Cascade programming environment supports MPI, OpenMP, pthreads, SHMEM and Global Arrays, as well as the global address space languages Unified Parallel C and Co-Array Fortran. For the most productive programming experience, Cascade supports global-view programming models, which provide a parallel programming experience more similar to uniprocessor programming. The new Chapel language provides data and control abstractions that simplify parallel programming and create a clean separation between high-level algorithms and low-level details such as data decomposition and layout. This enables a programmer to first focus on expressing the parallelism inherent in the algorithm being implemented, and later redefine the critical data structures to exploit locality and processor affinity.

#### The IBM PERC System

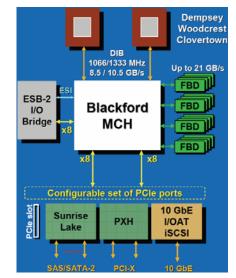

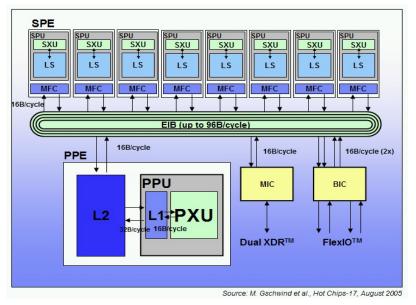

The Figures 1.3 and 1.4 highlight the key features of IBM's PERC system that is under development through the HPCS program.

### **IBM's Technical Approach for HPCS**

#### Unprecedented focus on productivity

- Hardware/software co-design focused on improving system productivity by more than an order of magnitude and significantly

expanding the number of productive users in a petascale environment

- Application development: programming models, languages, tools

- Administrative: automation, simplicity, ease of use

- A holistic approach that encompasses all the critical elements of supercomputer system architecture and design (Hardware and Software)

- Processors, Caches, Memory subsystem, networking, storage, Operating systems, parallel/cluster file systems, programming models, application development environment, compilers, tools for debugging and performance tuning, libraries, schedulers, checkpoint-restart, high availability software, systems management

- Balanced system architecture and design

- Leverage IBM leadership in UNIX systems to provide petascale systems on commercially viable technology

- POWER, AIX/Linux, ISVs, ...

- Focused effort on significantly enhancing the sustained performance experienced by applications at scale

Maximize compute time spent on productive computation by minimization of overhead

- Cluster network optimized for common communication patterns (collective, overlap of communication and computation...)

- Tools to identify and correct load imbalance

- General Purpose, flexible operating environment to address a large class of supercomputing applications

- Significant reductions in complexity and cost for large scale supercomputing infrastructure

#### Figure 1.3 IBM HPCS overview

IBM HPCS

#### **IBM Hardware Innovations**

- Next generation POWER processor with significant HPCS enhancements

- Leveraged across IBM's server platforms

- Enhanced POWER Instruction Set Architecture

- Significant extensions for HPCS

- Leverage the existing POWER software eco-system

- Integrated high speed network (very low latency, high bandwidth)

- Multiple hardware innovations to enhance programmer productivity

- Balanced system design to enable scalability

- Significant innovation in system packaging, footprint, power and cooling

Figure 1.4 IBM HPCS overview

As stated earlier, productivity, by its very nature, is difficult to assess because it depends upon the specifics of the end user mission, application, team composition, and end use or workflow. The challenge is to develop a productivity assessment strategy based on a mixture of qualitative and quantitative (preferred) analysis based metrics that will not only be used to evaluate the HPCS vendors but also adopted by the larger HPC community.

Figure 1.2 also shows a multi-year HPCS productivity initiative that was started in Phase II, funded by DARPA, DOE Office of Science, NNSA, NSA, and NSF, and led by Dr. Jeremy Kepner from MIT-Lincoln Laboratory. The Productivity Team was comprised of universities, laboratories, FFRDCs and HPCS Phase II vendors. Bi-annual public productivity conferences were held on a regular basis throughout the three year Phase II program. The HPCS Phase II Productivity Team projects can be loosely grouped as execution time and development time research elements. The next sections will delineate an expanded set of productive research elements and findings resulting from the HPCS Phase II Productivity Team projects. The representative research elements presented are performance benchmarking, system architecture modeling, productivity workflows/metrics and new languages.

In summary, the HPCS program represents a very unique partnership between DARPA, industry and the government end users (mission partners). Since this partnership represents a very different model from the past, what "it is not" is just as important as "what it intends" to be. The things the program is not are as follows:

- A One-off system. The HPCS system must be a viable commercial product.

- Meeting only one set of requirements. Aside from the varied requirements of the mission partners, the system must support a spectrum of a applications and configurations

- Available only at petascale. The system must scale from a single cabinet to very large configurations.

- Using only new languages. The HPCS system must also support existing programming languages, including C, C++ and Fortran and with MPI and existing PGAS languages.

#### 2. Productivity Systems Modeling

The HPCS vision centers around the notion of computing systems with revolutionary hardware-software architectures that will enable substantially higher productivity than projected continuations of today's evolutionary system designs. Certainly a crucial component of productivity is the actual ("sustained") performance the revolutionary computing systems will be able to achieve on applications and workloads. Because these architectures will incorporate novel technologies to an unusually large extent, predicting application performance will be considerably more difficult than is the case for next-generation systems based on evolutionary architectures. Hence, the availability of sophisticated performance modeling techniques will be critically important for designers of HPCS computing systems and for the success of the HPCS program as a whole.

Performance models allow users to predict the running time of an application based on the attributes of the application, its input, and the target machine. Performance models can be used by system architects to help design supercomputers that will perform well on assorted applications. Performance models can also inform users which machines are likely to run their application fastest, and to alert programmers to performance bottlenecks that they can then attempt to remove.

The *convolution problem* in performance modeling asks how to predict the performance of an application on different machines, based on two things: (1) machine profiles consisting of rates at which a computer can perform various types of operations as measured by simple benchmarks; and (2) an application signature consisting of counts of various types of operations performed by the application. The underlying notion is that the performance of an application can be represented by some combination of simple benchmarks measuring the ability of the target machine to perform different kinds of operations on the application's behalf.

There are three different methods for doing performance convolutions, each based on matrix operations, within the San Diego Supercomputing Center's Performance Modeling and Characterization (PmaC) framework for performance prediction. Each method is appropriate for answering a different set of questions related to correlating application performance to simple benchmark results. Each requires a different level of human insight and intervention. And each, in its own way, can be used to predict the performance of applications on machines where the real runtime is unknown.

The first method uses Least Squares fitting to determine how good a statistical fit can be made between observed runtimes of applications on different machines, using a set of machine profiles (measured by using simple benchmarks); the resulting application signatures can then be used within the framework for performance prediction. This method has the virtue of being completely automated.

The second method uses Linear Programming to fit the same input data as the first method (or similar input data). In addition, however, it can also mark input machine profiles and/or application runtimes as suspect. This corresponds to the real world

situation in which one wants to make sense out of benchmarking data from diverse sources, including some that may be flawed. While potentially generating more accurate application signatures that are better for performance prediction, this method requires some user interaction. When the solver flags data as suspect, the user must either discard the data, correct it, or insist that it is accurate.

Instead of inference from observed application runtimes, the third method relies on instrumented application tracing to gather application signatures directly. While arguably the most general-purpose and accurate of the three methods, it is also the most labor intensive. The tracing step is expensive compared to measuring the un-instrumented application runtimes, as used by the Least Squares and Linear Programming methods to generate application signatures. Moreover, unlike the first two methods, forming the performance model requires substantial expert interaction to "train" the convolution framework, though subsequently performance predictions can be done automatically.

Finally we demonstrate how a judicious mix of these methods may be appropriate for large performance modeling efforts. The first two allow for broad workload and HPC asset characterizations, such as understanding what system attributes discriminate performance across a set of applications, while the last may be more appropriate for very accurate prediction and for guiding tuning efforts. To evaluate these methods, we tested them on a variety of HPC systems and on applications drawn from the Department of Defense's Technical Insertion 2006 (TI-06) application workload [5].

#### 2.1 Problem Definition and Unified Framework

As an example of a simple pedagogical convolution, consider Equation 1. Equation 1 predicts the runtime of application a on machine m by combining three of application a 's operation counts (the number of floating-point, memory and communication operations) with the corresponding rates at which machine m can perform those operations.

$$\operatorname{Runtime}_{a,m} \approx \frac{\operatorname{FloatOps}_{a}}{\operatorname{FloatOpRate}_{m}} + \frac{\operatorname{MemoryOps}_{a}}{\operatorname{MemoryOpRate}_{m}} + \frac{\operatorname{CommOps}_{a}}{\operatorname{TransferRate}_{m}}$$

(1)

In practice, FloatOpRate, MemoryOpRate and TransferRate could be determined by running a set of simple synthetic benchmarks such as HPL, STREAM, and EFF\_BW, respectively, from the HPC Challenge benchmarks [10]. Likewise, FloatOps, MemoryOps, and CommunicationOps could be measured for the application using hardware and software profiling tools such as the PMaC MetaSim Tracer [3] for floating and memory operations, and MPIDTrace [1] for communication events.

We could generalize Equation 1 by writing it as in Equation 2, where OpCount represents a vector containing the three operation counts for application a, Rate is a vector containing the corresponding three operation rates for machine m, and  $\oplus$  represents a generic operator. This generic operator could, for example, take into account a machine's ability to overlap the execution of two different types of operations.

$$\text{Time}_{a,m} \approx P_{a,m} = \frac{\text{OpCount}(1)}{\text{Rate}(1)} \oplus \frac{\text{OpCount}(2)}{\text{Rate}(2)}$$

$$\oplus \frac{\text{OpCount}(3)}{\text{Rate}(3)}$$

(2)

If the number of operation counts used in Equation 2 is expanded to include other performance factors, such as the bandwidth of strided accesses to L1 cache, the bandwidth of random-stride accesses to L1 cache, the bandwidth of strided accesses to main memory, network bandwidth, etc., we could represent application a's operation counts by making OpCount a vector of length c, where c is the total number of different operation types represented for application a. We could further expand OpCount to represent more than one application by making OpCount a matrix of dimension  $c \times n$ , where *n* is the total number of applications characterized. Similar expansion could be done for Rate, making it a  $k \times c$  matrix, where k is the total number of machines, each of which is characterized by c operation rates. This would make P a  $k \times n$  matrix in which  $P_{ij}$  is the predicted runtime of application *i* on machine *j*. That is, the generalized Equation 2 represents the calculation of predicted runtimes of n different applications on k different machines and can be expressed as  $P = \text{Rate} \otimes \text{OpCount}$ . Since each column in OpCount can also be viewed as the application signature of a specific application, we refer to OpCount as the application signature matrix, A. Similarly, each row of Rate is the machine profile for a specific machine, and so we refer to Rate as the machine profile matrix, M. Now the convolution problem can be written as  $P = M \otimes A$ . In expanded form, this looks like:

$$\begin{bmatrix} p_{1,1} & \dots & p_{1,n} \\ p_{2,1} & \dots & p_{2,n} \\ p_{3,1} & \dots & p_{3,n} \\ \vdots & \ddots & \vdots \\ p_{k,1} & \dots & p_{k,n} \end{bmatrix} = \begin{bmatrix} m_{1,1} & \dots & m_{1,c} \\ m_{2,1} & \dots & m_{2,c} \\ m_{3,1} & \dots & m_{3,c} \\ \vdots & \ddots & \vdots \\ m_{k,1} & \dots & m_{k,c} \end{bmatrix} \otimes \begin{bmatrix} a_{1,1} & \dots & a_{1,n} \\ \vdots & \ddots & \vdots \\ a_{c,1} & \dots & a_{c,n} \end{bmatrix}$$

(3)

Given Equation 3 as the general convolution problem, the relevant questions are how to determine the entries of M and A, and what to use for the  $\otimes$  operator to generate accurate performance predictions in P?

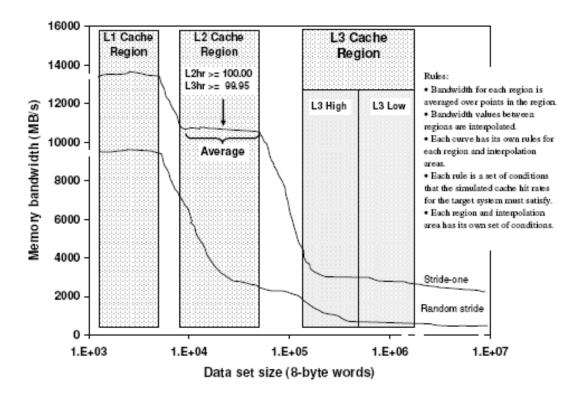

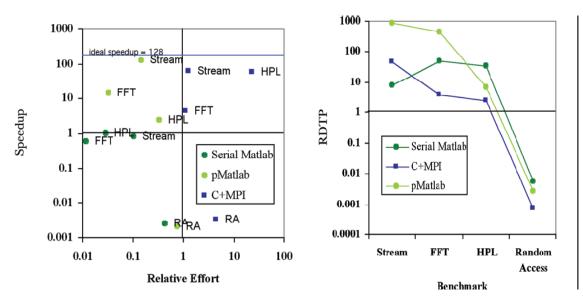

Populating M is fairly straightforward, at least if the machine or a smaller prototype for the machine exists. Traditionally, this has been done by running simple benchmarks. It should be noted that determining c, the smallest number of benchmarks needed to accurately represent the capabilities of the machine, is generally considered an open research problem [3]. In this work, to populate M, we used the *netbench* and *membench* synthetic benchmarks from the TI-06 benchmark suite [22]. These benchmarks can be considered a superset of the HPC Challenge Benchmarks. For example, Figure 2 plots the results of running membench on an IBM system. We could then populate M with several memory bandwidths corresponding to L1 cache bandwidth for strided loads, L1-L2 (an intermediate bandwidth), L2 bandwidth, etc., to represent the machine's capabilities to service strided load requests from memory; similarly, rates for random access loads, stores of different access patterns, floating-point and communication operations can be included in M. One could think of the upper curve in Figure 2 as giving the results of running the STREAM benchmark from the HPC Challenge Benchmarks at different sizes ranging from small to large, and the lower curve as the serial version of the RandomAccess benchmark run in the same way. (Some implementation details differ between the TI-06 synthetics and HPC Challenge, but the overall concepts and the rates they measure are the same.)

Populating A is less straightforward. While traditionally users have consulted performance counters to obtain operation counts, this may not reveal important operation subcategories such as the access pattern or locality of memory operations. For example, we can see from Figure 2 that not all memory operations are equal; rates at which machines can complete memory operations may differ by orders-of-magnitude, depending on where in the memory hierarchy they fall. An alternative to performance counters is application tracing via code instrumentation. Tracing can, for example, discover memory addresses and locality, but is notoriously expensive [7]. The methods we propose in this section find the entries of A using three different methods, each with different tradeoffs in accuracy versus effort.

#### 2.2 Methods to Solve the Convolution Problem

In this work, we investigate three methods for calculating A and determining the  $\otimes$  operator. We classify the first two methods as *empirical* and the third one as *ab initio*. Empirical methods assume M and some values of P are known, and then derive the matrix A. Matrix A can then be used to generate more values of P. Ab initio methods, on the other hand, assume both M and A are known and then calculate P from first principles. In addition to this classification, the first two methods may be considered *top down* in that they attempt to resolve a large set of performance data for consistency, while the last may be considered *bottom up* as it attempts to determine general rules for performance modeling from a small set of thoroughly characterized loops and machine characteristics.

#### 2.2.1 Empirical Method

Although traditionally we assume P is unknown and its entries are to be predicted by the model, in practice some entries of P are always measured directly by timing application runs on real machines. This may be done simply to validate a prediction, although the validation may be done some time in the future, as is the case when predicting runtimes on proposed machines. A key observation is that running an application on an existing machine to find an entry of P is generally significantly easier than tracing an application to calculate the P entry through a model. This suggests that we treat some entries of P as known for certain existing systems and M as also known via ordinary benchmarking effort, rather than treating P as an unknown and A as knowable only via extraordinary tracing effort. This, combined with assumptions about the structure of the convolution operator  $\otimes$ , allows us to solve for A. Once A is known for the applications of interest, it can be convolved with a new M' to predict performance on these other machines, where

M' is just M with rows for the new machines, for which simple synthetic benchmarks may be known or estimated but for which full application running times are unknown.

We refer to the methods that treat *A* as the unknown as *empirical* in the sense that one can deduce the entries of a column of *A* by observing application runtimes on a series of machines that differ by known quantities in their ability to perform operations in each category. As an example, intuitively, if an application has very different runtimes on two systems that are identical except for their network latency, we may deduce that the application's sensitivity to network latency comes from the fact that it sends numerous small messages.

We formalize this intuition and demonstrate two different techniques for empirical convolution. In both methods we assume that there is a set of machines on which we have gathered not only the synthetic benchmarks used to fill in the matrix M, but also actual runtimes for n applications of interest in P. We further assume that the operator  $\otimes$  is the matrix multiplication operator. We now describe two different approaches for using P and M to solve for entries of the application matrix, A, within a reasonable range of error.

The first empirical approach uses Least Squares to find the entries of A, and is particularly appropriate when the running times are known on more machines than we have benchmark data for. The second empirical approach uses Linear Programming to find the entries of A and can be useful in the under-constrained case where we have real runtimes on fewer machines than we have benchmark data for. In addition to finding entries in the application matrix A, both methods can also be used to address questions such as:

- What is the best fit that can be achieved with a given assumption about the convolution? (For example, we may assume the convolution operator is a simple dot-product and operation counts are machine-independent for each application.)

- Can one automatically detect outliers, as a way to gain insight into the validity of benchmark and runtime data from various sources?

- Can one calculate application weights for a subset of the systems and use those weights to accurately predict runtimes on other systems?

- What properties of systems are most important for distinguishing their performance?

#### **2.2.2 Solving for** *A* **using Least Squares**

Consider solving the matrix equality P = MA for A. We can solve for each column of A individually (i.e.,  $P_i = MA_i$ ), given the (plausible) assumption that the operation counts of one application do not depend on those of another application. If we further decide to

compute application operation counts that minimize the 2-norm of the residual  $P_i - MA_i$ , then the problem becomes the much-studied Least-Squares problem. Furthermore, because only non-negative application operation counts have meaning, we can solve  $P_i = MA_i$  as a nonnegative Least Squares problem. These problems can be solved by a technique described in [9] and implemented as lsqnonneg in Matlab. In practice, before applying the nonnegative Least Squares solver, we normalize both the rows and columns of the equation with respect to the largest entry in each column. Rescaling the columns of M so that the largest entry in each column is 1 allows us to weight different operations similarly, despite the fact that the cost of different types of operations can vary by orders of magnitude (e.g., network latency versus time to access the L1 cache). Rescaling the rows of M and  $P_i$  so that the entries of P are all 1 allows us to normalize for different runtimes.

The Least Squares approach has the advantage of being completely automatic, as there are no parameters to change or constraints that may need discarding. Thus, it also partially answers the question: if all the benchmark and runtime data are correct, how well can we explain the running times within the convolution framework? However, if some of the data is suspect, the Least Squares method will attempt to find a compensating fit rather than identifying the suspect data.

#### 2.2.3 Solving for A using Linear Programing

Unlike the Least Squares Method that seeks the minimum quadratic error directly, the Linear Programming Method is more subtle — and it can also be more revealing. There are various ways to rephrase Equation 3 as a Linear Programming problem; in our implementation, for every *i* and *j* ( $1 \le i, j \le n$ ), Equation 3 is relaxed to yield the following two inequalities:

$$p_{ij} \cdot (1 - \beta) \ge m_i \oplus a_j$$

$$p_{ij} \cdot (1 - \beta) \le m_i \oplus a_j$$

where  $0 < \beta < 1$  is an arbitrary constant and each element  $a_j$  is a non-negative variable.

Therefore, each pair of inequalities defines a stripe within the solution space, and the actual solution must lie within the intersection of all n stripes. Should any stripe fall completely outside the realm of the others, no solution that includes that machine-application pair exists. Given a simplifying assumption that similar architectures have similar frequencies of operations per type for a given application, it is expected that the intersection of the stripes will not be null, since the application execution time  $p_{ii}$  will

likely be a direct result of synthetic capability  $m_i$  (when neglecting more complex, possibly non-deterministic execution properties such as overlapping operations, pre-fetching, and speculative execution). A null solution, therefore, suggests that an error may lie in one of the execution times or one of the synthetic capability measurements.

To determine the "optimal" solution for  $a_j$ , the intersection of all stripes must result in a bounded space. In such a case, the intersection vertices are each tested via an objective function to determine the best solution. For this implementation, a minimum is sought for

$$f(a_j) = \sum_{i=1}^k (m_i \oplus a_j)$$

(4)

in order to force the estimate for the application times to be inherently faster than the actual application times. The error for each may then be associated with operation types such as I/O reads and writes that are not represented in the set of basic operations.

In applying the Linear Programming method, the value for  $\beta$  was increased until all stripe widths were sufficiently large, in order to achieve convergence. Estimates for the application times were then calculated for each machine (1) to determine the overall extent of the estimation error and (2) to identify any systems with outlying error values when clustering error percentages using a nearest-neighbor technique. Any system identified in (2) was removed from consideration, since an error in its application or synthetic benchmarks was suspected. This methodology was applied iteratively until the minimum value for  $\beta$  that achieved convergence and the overall estimation error were both considered to be small.

#### 2.2.4 Ab Initio Method

Methods that assume *P* is unknown are referred to here as *ab initio*, in the sense that the performance of an application running on a the system is to be determined from its first principles. The assumption, then, is that both *M* and *A* are known but the generic  $\otimes$  operator and *P* are not known.

To separate concerns we split the problem of calculating P into two steps. The first step is to predict the execution time of the parallel processors between communication events. Following the format of Equation 3, memory and floating-point operations are gathered by tracing and are further fed through a simulator to propagate the corresponding entries of a matrix A'. Each column of A' then holds floating-point operations and memory operations (but not communication operations), broken down into different types, access patterns, locality, etc., for a particular application. P' is obtained by multiplying A' with M, and thus a row of P' represents the application's predicted time spent doing work on-processor during execution on the machines of M. In the second step, the Dimemas [6] simulator processes the MPI trace data and P' in order to model the full parallel execution time. The output from Dimemas is then the final calculated execution time for the application(s) on the target machine(s) (P).

In the remainder of this section, we describe how the trace data is used to determine the entries of A' and how A' is used to calculate the entries of P'. Since the time spent doing floating-point operations tends to be small compared to the time spent doing memory operations in large scale parallel applications, we focus on describing how we determine the entries of A' related to memory performance.

Our approach is to instrument and trace the applications using the PMaC MetaSim Tracer, and then to use the PMaC MetaSim Convolver to process the traces in order to find the entries in A'. Details of the PMaC MetaSim Tracer and the processing of the trace by the PMaC MetaSim Convolver can be found in [19].

Before preceding it is important to note that the ab initio methods relax two constraints of the Least Squares and Linear Programming methods. First, an application's trace, particularly its memory trace, is fed to a cache simulator for the machine(s) to be predicted. This means a column of A' can be different on different machines., This represents a notable sophistication over the empirical methods: it is no longer assumed that operation category counts are the same on all machines (for example, machines with larger caches will get more operations that hit in cache). Second, rather than assuming a simple combining operator such as a dot product, the convolver can be trained to find a better operator that predicts performance with much smaller prediction errors. This operator may, for example, allow overlapping of floating-point operations with memory operations – again a notable advance in sophistication that is more realistic for modern machines.

Since tracing is notoriously expensive, we employ cross-platform tracing in which the tracing is done only once on a single system, but the cache structure of many systems is simulated during tracing. Figure 1 shows some of the information that MetaSim Tracer collects for every basic block (a basic block is a straight run of instructions between branches) of an application. Fields that are assumed under the cross-platform tracing assumption to be the same across all machines are collected or computed from direct observation; but fields in the second category are calculated by feeding the dynamic address stream on-the-fly to a set of cache simulators, unique to each machine.

The MetaSim Convolver predicts the memory performance of each basic block by mapping it to some linear combination of synthetic benchmark memory performance results (entries of M) using the basic block fields, such as simulated cache hit rates and stride access pattern, as shown in Figure 2.1. This convolver mapping is implemented as a set of conditions to be applied to each basic block to determine which bandwidth region and curve of Figure 2.1 to use for its estimated performance. A sample of one of these conditions for the L2 cache region on the ARL P690 system is shown on Figure 2.1. The main advance on this method described in this work is to refine these conditions to improve prediction accuracy as described next. The rules in Figure 2.1 further exemplify the conditions that were developed for each region and interpolation area between regions of the membench curves.

Figure 2.1. The strided (upper) and random (lower) memory bandwidth test from membench taken from an IBM P690 system at Army research Laboratory (ARL), along with example rules for mapping a basic-block to its expected memory performance.

In order to determine and validate the best set of conditions for minimizing prediction error, a small experimental  $P^{measured} = MA'$  problem was defined. We chose several computational loops as a "training set" to develop and validate the convolving conditions. We chose 40 computational loops from two parallel applications, HYCOM and AVUS, from the TI-06 application suite; then execution times for these loops on 5 systems were measured to propagate the entries of  $P^{measured}$ . The loops were chosen judiciously, based on their coverage of the trace data space: their constituent basic blocks contain a range of hit rates, different randomness, etc. We then performed a human-guided iteration, trying different sets of conditions the MetaSim Convolver could implement to determine each loop's A' and thence entries in  $P^{predicted}$ . Thus, we were looking for rules to map basic blocks to expected performance; the rules were constrained to make sense in terms of first principles properties of the target processors. For example, a loop's memory work cannot obtain higher than measured L1 memory performance, or lower than measured main memory performance. More subtly, the L1 hit rate value required to assign a basic block to get L1 cache performance could not be less than the hit rate value that would assign L3 cache performance.

We sought then to determine conditions in such a way that the generated elements of A' would produce the most accurate calculated  $P^{predicted}$ . In other words, we looked for conditions to minimize:

$$\text{Total error} = \sum_{i,j}^{m,n} |(P_{i,j}^{\text{measured}} - P_{i,j}^{\text{predicted}})/P_{i,j}^{\text{measured}}|$$

(5)

where m is the number of machines (5) and n is the number of loops (40).

Finally, having developed the conditions for the training set that minimized total error, we used the same conditions to convolve and to predict the full AVUS and HYCOM applications, as well as a larger set of applications on a larger set of machines.

#### **2.2.5 Experimental Results**

To evaluate the usefulness of the *empirical* and *ab initio* methods, we tested both on several strategic applications run at several processor counts and inputs on the systems listed in Table 2.1. We chose several applications from the Technical Insertion 2006 (TI-06) application workload that covered an interesting space of computational properties, such as ratio of computation to communication time, ratio of floating-point operations to memory operations, and memory footprint size. None of these codes on the inputs given are I/O intensive; thus we do not model I/O in the remainder.

The applications used are AVUS, a code used to determine the fluid flow and turbulence of projectiles and air vehicles; CTH, which models complex multidimensional, multiplematerial scenarios involving large deformations or strong shock physics; HYCOM, which models all of the world's oceans as one global body of water; OVERFLOW, which is used for computation of both laminar and turbulent fluid flows over geometrically complex, non-stationary boundaries; and WRF, which is a next-generation mesoscale numerical weather prediction system designed to serve both operational forecasting and atmospheric research needs.

The applications were run on two different inputs each (DoD designations "Standard" and "Large") and on 3 different processor counts between 32 and 512 for each input on all 20 of the systems listed. More information on these applications can be found at [3] and [5]. It should be clear that populating the  $P^{measured}$  matrix for the Least Squares and Linear Programming methods required in this case measuring about 600 application runtimes (20 systems, 5 applications, 2 inputs each, 3 cpu counts each). These are full applications that run, on average, about one or two hours each, depending on input and cpu count. The  $P^{measured}$  values were therefore collected by a team of people from the Department of Defense High Performance Computing Modernization Program (HPCMP) centers. The authors populated the M matrix by running the membench and netbench benchmarks on these same systems.

In testing the empirical methods, we tried several variants of the M matrix, in part to explore the relationship between the number of columns in M (and rows in A) and the resulting accuracy. This complements investigations in [3], where the authors studied the

smallest number of benchmarks required to accurately represent the capabilities of machines. For example, we tried 10- and 18-column variants of the M matrix, both based on the same machine benchmark data. The one with 10 columns had 8 measures pertaining to the memory subsystem from membench (i.e., drawn from plots similar to Figure 2.1), and 2 being the off-node bandwidth and the latency of the interconnect from netbench, as described above. The set with 18 columns had 14 measures pertaining to the memory subsystem (i.e., taking more points from the membench curve in Figure 2.1), 2 for off-node bandwidth and latency, and 2 for on-node bandwidth and latency. From the synthetic measures pertaining to the memory subsystem, half were chosen from strided membench results and the other half were chosen from random access membench results.

We now discuss the data in Table 2.1, which summarizes the results of using the empirical methods to understand our data set.

| Error Summary       | Average<br>Absolute<br>Error |

|---------------------|------------------------------|

| Systems             | LS LP                        |

| ASC_SGI_Altix       | 4% 8%                        |

| SDSC_IBM_IA64       | 12%—                         |

| ARL_IBM_Opteron     | 12%8%                        |

| ARL_IBM_P3          | 4% 4%                        |

| MHPCC_IBM_P3        | 6% 6%                        |

| NAVO_IBM_P3         | 9% 6%                        |

| NAVO_IBM_p655 (Big) | 5% 6%                        |

| NAVO_IBM_p655 (Sml) | 5% 5%                        |

| ARSC_IBM_p655       | 4% 2%                        |

| MHPCC_IBM_p690      | 8% 7%                        |

| NAVO_IBM_p690       | 7% 9%                        |

| ARL_IBM_p690        | 10%6%                        |

| ERDC_HP_SC40        | 6% 8%                        |

| ASC_HP_SC45         | 5% 4%                        |

| ERDC_HP_SC45        | 5% 6%                        |

| ARSC_Cray_X1        | 8% 5%                        |

| ERDC_Cray_X1        | 51%3%                        |

| AHPCRC_Cray_X1E     | 14%—                         |

| ARL_LNX_Xeon (3.06) | 6% 8%                        |

| ARL_LNX_Xeon (3.6)  | 16%8%                        |

| Overall Error       | % %                          |

#### 2.2.6 Fitting the data using Least Squares

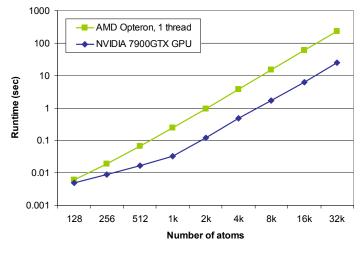

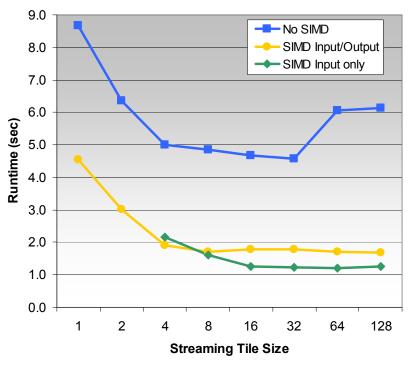

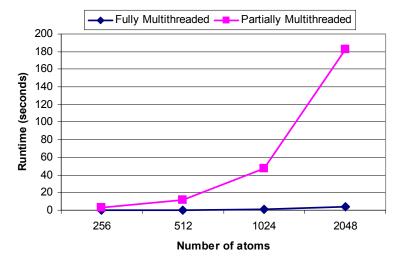

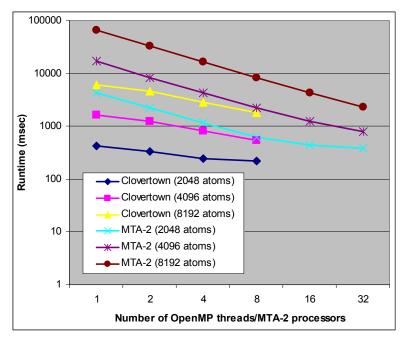

Table 2.1. Average absolute error for all applications tested on 20 DoDsystems. Format of column 1 is acronym of Department of Defensecomputer center-computer manufacturer-processor type.