# Overview of recent supercomputers

Aad J. van der Steen Computational Physics Utrecht University P.O. Box 80000, 3508 TA Utrecht Email: steen@fys.ruu.nl

# Publication of the NCF

Stichting Nationale Computer Faciliteiten P.O. Box 93120 2509 AC 's-Gravenhage The Netherlands Seventh revised edition

January 1997

#### Abstract

In this report we give an overview of parallel and vector computers which are currently available or will become available within a short time frame from vendors; no attempt is made to list all machines that are still in the research phase. The machines are described according to their architectural class. Shared and distributed memory SIMD and MIMD machines are discerned. The information about each machine is kept as compact as possible. Moreover, no attempt is made to quote prices as these are often even more elusive than the performance of a system.

This document reflects the technical state of the supercomputer arena as accurately as possible. However, the author nor NCF take any responsibility for errors or mistakes in this document. We encourage anyone who has comments or remarks on the contents to inform us, so we can improve this work.

NCF, the National Computing Facilities Foundation, supports and furthers the advancement of technical and scientific research with and into advanced computing facilities and prepares for the Netherlands national supercomputing policy. Advanced computing facilities are multi-processor vectorcomputers, massively parallel computing systems of various architectures and concepts and advanced networking facilities.

# Contents

| 1        | Intro | oduction and account                                   | 3               |

|----------|-------|--------------------------------------------------------|-----------------|

| <b>2</b> |       | nitecture of high performance computers                | <b>5</b>        |

|          |       | The main architectural classes                         | 5               |

|          |       | Shared-memory SIMD machines                            | 6               |

|          |       | Distributed-memory SIMD machines                       | 7               |

|          | 2.4   | Shared-memory MIMD machines                            | 9               |

|          | 2.5   | Distributed-memory MIMD machines                       | 11              |

| 3        | Reco  | ount of the (almost) available systems                 | 13              |

|          |       |                                                        | 13              |

|          |       |                                                        | 13              |

|          |       |                                                        | 15              |

|          |       |                                                        | 15              |

|          |       |                                                        | 16              |

|          |       |                                                        | 17              |

|          |       |                                                        | 18              |

|          |       |                                                        | 19              |

|          |       |                                                        | 19<br>19        |

|          |       |                                                        | $\frac{19}{20}$ |

|          |       |                                                        | $\frac{20}{21}$ |

|          |       |                                                        |                 |

|          |       |                                                        | 21              |

|          |       |                                                        | 22              |

|          |       |                                                        | 23              |

|          |       | U U                                                    | 25              |

|          |       |                                                        | 25              |

|          |       | v                                                      | 26              |

|          |       |                                                        | 26              |

|          |       | v                                                      | 27              |

|          |       | 5                                                      | 28              |

|          |       | 5                                                      | 29              |

|          |       |                                                        | 30              |

|          |       | 3.4.8 The HP/Convex Exemplar SPP-2000 series           | 31              |

|          | ;     | 3.4.9 The IBM 9076 SP2                                 | 32              |

|          |       |                                                        | 33              |

|          | ;     | 3.4.11 The Kongsberg Informasjonskontroll SCALI system | 34              |

|          | ;     |                                                        | 34              |

|          | ;     | 3.4.13 The Meiko Computing Surface 2                   | 35              |

|          |       | 3.4.14 The nCUBE 2S                                    | 36              |

|          |       |                                                        | 37              |

|          | ;     | ·                                                      | 38              |

|          |       |                                                        | 39              |

|          |       |                                                        | 40              |

|          |       |                                                        |                 |

| 4        | Syste | ems disappeared from the list                          | 41              |

| <b>5</b> | Syste | ems under development                                  | <b>45</b>       |

|          | 5.1 ( | The Hitachi/CP-PACS system                             | 45              |

|          | 5.2   | Machines in the ASCI program                           | 45              |

|          |       |                                                        | 45              |

|          |       |                                                        | 46              |

|          |       | -                                                      | 46              |

|          |       | v v                                                    |                 |

# Acknowledgments

Bibliography

# 1 Introduction and account

This is the seventh edition of a report in which we attempt to give an overview of parallel and vector systems that are commercially available or are expected to become available within a short time frame (typically a few months to half a year). We choose the expression "attempt" deliberately because the market of paralleland vector machines is highly evasive: the rate with which systems are introduced — and disappear again — is very high and therefore the information will probably be only approximately valid. Nevertheless, we think that such an overview is useful for those who want to obtain a general idea about the various means by which these systems strive at high performance, especially when it is updated on a regular basis.

We will try to be as up-to-date and compact as possible and on these grounds we think there is a place for this report. Like last year, the present report will be somewhat shorter than earlier ones: at this moment systems are disappearing at a faster rate than new ones replace them. The reasons for this seem to be threefold:

- The competition is very fierce and only companies that can offer up-to-date systems, both hardware and software wise can keep in business.

- Generally, less money is available worldwide for purchasing new high performance systems oriented to scientific and technical computing. This makes life more difficult for both existing companies and for potential starters.

- Because of price/performance considerations the number of companies offering systems with custommade processors is decreasing because they cannot capitalise on large volume sales as is the case with RISC processor based systems.

These effects make the high performance computing scene somewhat more clear (and also somewhat less adventurous). Still, the supercomputer market is very dynamic and we cannot hope to give a complete report for the reason already mentioned above: the speed with which companies and systems appear and disappear makes this almost impossible. However, by updating the report we can at least follow the main trends in popular and emerging architectures.

The rules for including systems in this report are as follows: they should be either available commercially at the time of appearance of this report, or within 6 months thereafter. This excludes interesting research systems like the Intel ASCI Option Read system at Sandia National Laboratory (with a measured performance just over 1 Tflop/s), the CP-PACS at the University of Tsukuba (measured performance of 368 Gflop/s), and the Numerical Windtunnel at the National Aeroscape Lab. in Japan (230 Gflop/s), because they are not marketed and only available at the institutes mentioned and therefore of not much benefit to the supercomputer user community at large.

The rule that systems should be available within a timespan of 6 months is to avoid confusion by describing systems that are announced much too early, just for marketing reasons and that will not be available to general users within a reasonable time. We also have to refrain from including all generations of a system that are still in use. Therefore, for instance, we do not include the Convex C3000 series, the Cray Y-MP series, or the Thinking Machines CM-5 anymore although these systems are still used widely. Generally speaking, we include machines that are still marketed or will be marketed within 6 months. To add to the information given in this report, we quote the Web addresses of the vendors because the information found there may be more recent than what can be provided here. On the other hand, such pages should be read with care because it will not always be clear what the status is of the products described there.

Some vendors offer systems that are identical in all respects except in the clock cycle of the nodes (examples are the Digital Alphaserver and the Fujitsu AP3000). In these cases we always only mention the models with the fastest clock as it will be always possible to get the slower systems and we presume that the reader is primarily interested in the highest possible speeds that can be reached with these systems.

We order the systems by their various architectural classes, which should facilitate to find the information of systems that belong to a certain class. We also omit the price information which in most cases is next to useless. If available, we will give some information about performances of systems based on user experiences instead of only giving theoretical peak performances. Here we have adhered to the following policy: We try to quote *best measured performances*, if available, thus providing a more realistic upper bound than the theoretical peak performance. We hardly have to say that the speed range of supercomputers is enormous, so the best measured performance will not always reflect the performance of the reader's favourite application. When we give performance information, it is not always possible to quote all sources and in any case if this information seems (or is) biased, this is entirely the responsibility of the author of this report. He is quite willing to be corrected or to receive additional information from anyone who is in the position to do so.

Before giving a recount of the systems proper, we first define the architectural classes and some other terms in section 2 which will be used in section 3 in the description of the machines. In section 4 some systems are listed that disappeared from the market and in section 5 we present some systems that are under development and have a fair chance to appear on the market.

The overview given in this report concentrates on the computational capabilities of the systems discussed. To do full justice to all assets of present days high-performance computers one should list their I/O performance and their connectivity possibilities as well. However, the possible permutations of configurations even for one model of a certain system often are so large that they would multiply the volume of this report, which we tried to limit for greater clarity. So, not all features of the systems discussed will be present. Still we think (and certainly hope) that the impressions obtained from the entries of the individual machines may be useful to many. We also omitted some systems that may be characterised as "high-performance" in the fields of database management, real-time computing, or visualisation. Therefore, as we try to give an overview for the area of general scientific and technical computing, systems that are primarily meant for database retrieval like the AT&T GIS systems or concentrate exclusively on the real-time user community, like Concurrent Computing Systems, are not discussed in this report.

Although most terms will be familiar to many readers, we still think it is worthwhile to give some of the definitions in section 2 because some authors tend to give a meaning that may slightly differ from the idea the reader already may have acquired.

Lastly, we should point out that also a WWW version is available. The URLs are: www.netlib.org/utk/papers/advanced-computers/paper.html (USA) www.sara.nl/nwo/ncf/(Europe)

# 2 Architecture of high performance computers

Before going on to the descriptions of the machines themselves, it is important to consider some mechanisms that are or have been used to increase the performance. The hardware structure or *architecture* determines to a large extent what the possibilities and impossibilities are in speeding up a computer system beyond the performance of a single CPU. Another important factor that is considered in combination with the hardware is the capability of compilers to generate efficient code to be executed on the given hardware platform. In many cases it is hard to distinguish between hardware and software influences and one has to be careful in the interpretation of results when ascribing certain effects to hardware or software peculiarities or both. In this chapter we will give most emphasis to the hardware architecture. For a description of machines that can be considered to be classified as "high-performance" one is referred to [20] and, for more recently available systems, [19].

# 2.1 The main architectural classes

Since many years the taxonomy of Flynn [6] has proven to be useful for the classification of high-performance computers. This classification is based on the way of manipulating of instruction and data streams and comprises four main architectural classes. We will first briefly sketch these classes and afterwards fill in some details when each of the classes is described.

- SISD machines: These are the conventional systems that contain one CPU and hence can accommodate one instruction stream that is executed serially. Nowadays many large mainframes may have more than one CPU but each of these execute instruction streams that are unrelated. Therefore, such systems still should be regarded as (a couple of) SISD machines acting on different data spaces. Examples of SISD machines are for instance most workstations like those of DEC, Hewlett-Packard, and Sun Microsystems. The definition of SISD machines is given here for completeness' sake. We will not discuss this type of machines in this report.

- SIMD machines: Such systems often have a large number of processing units, ranging from 1,024 to 16,384 that all may execute the same instruction on different data in lock-step. So, a single instruction manipulates many data items in parallel. Examples of SIMD machines in this class are the CPP DAP Gamma and the MasPar MP-2.

Another subclass of the SIMD systems are the vector processors. Vector processors act on vectors of similar data rather than on single data items using specially structured CPUs. When data can be manipulated by the vector units contained in these CPUs, results can be delivered with a rate of one, two and — in special cases — of three per clock cycle (a clock cycle being defined as the basic internal unit of time for the system). So, vector processors execute on their data in an almost parallel way but only when executing in vector mode. In this case they are several times faster than when executing in conventional scalar mode. For practical purposes vector processors with one CPU are therefore mostly regarded as SIMD machines. Examples of such systems are for instance the Convex C410, and the Hitachi S3600.

- MISD machines: Theoretically in these type of machines multiple instructions should act on a single stream of data. As yet no practical machine in this class has been constructed nor are such systems easily to conceive. We will disregard them in the following discussions.

- MIMD machines: These machines execute several instruction streams in parallel on different data. The difference with the multi-processor SISD machines mentioned above lies in the fact that the instructions and data are related because they represent different parts of the same task to be executed. So, MIMD systems may run many sub-tasks in parallel in order to shorten the time-to-solution for the main task to be executed. There is a large variety of MIMD systems and especially in this class the Flynn taxonomy proves to be not fully adequate for the classification of systems. Systems that behave very differently like a four-processor Cray Y-MP T94 and a thousand processor nCUBE 2S fall both in this class. In the following we will make another important distinction between classes of systems and treat them accordingly.

- Shared memory systems: Shared memory systems have multiple CPUs all of which share the same address space. This means that the knowledge of where data is stored is of no concern to the user as there is only one memory accessed by all CPUs on an equal basis. Shared memory systems can be both SIMD or MIMD. Single-CPU vector processors can be regarded as an example of the former, while the multi-CPU models of these machines are examples of the latter. We will sometimes use the abbreviations SM-SIMD and SM-MIMD for the two subclasses.

- Distributed memory systems: In this case each CPU has its own associated memory. The CPUs are connected by some network and may exchange data between their respective memories when required. In contrast to shared memory machines the user must be aware of the location of the data in the local memories and will have to move or distribute these data explicitly when needed. Again, distributed memory systems may be either SIMD or MIMD. The first class of SIMD systems mentioned which operate in lock step, all have distributed memories associated to the processors. For the distributed memory MIMD systems again a subdivision is possible: those in which the processors are connected in a fixed topology and those in which the topology is flexible and may vary from task to task. For the distributed memory systems we will sometimes use DM-SIMD and DM-MIMD to indicate the two subclasses.

Although the difference between shared- and distributed memory machines seems clear cut, this is not always entirely the case from user's point of view. For instance, the late Kendall Square Research systems employed the idea of "virtual shared memory" on a hardware level. Virtual shared memory can also be simulated at the programming level: A specification of High Performance Fortran (HPF) was published in 1993 [11] which by means of compiler directives distributes the data over the available processors. Therefore, the system on which HPF is implemented in this case will look like a shared memory machine to the user. Other vendors of Massively Parallel Processing systems (the buzz-word MPP systems is fashionable here), like Convex and Cray, also support proprietary virtual shared-memory programming models which means that these physically distributed memory systems, by virtue of the programming model, logically will behave as shared memory systems. In addition, packages like TreadMarks ([1]) provide a virtual shared memory environment for networks of workstations.

Another trend that has come up in the last few years is *distributed processing*. This takes the DM-MIMD concept one step further: instead of many integrated processors in one or several frames, workstations, mainframes, etc., are connected by standard network protocols like Ethernet, FDDI, or otherwise and set to work concurrently on tasks in the same program. Conceptually, this is not different from DM-MIMD computing, but the communication between processors is often orders of magnitude slower. Many packages to realise distributed computing, commercial, and non-commercial are available. Examples of these are PVM (standing for Parallel Virtual Machine) [7], and MPI (Message Passing Interface, [8, 15]). PVM and MPI have been adopted for instance by Convex, Cray, IBM and Intel for the transition stage between distributed computing and MPP on the clusters of their favorite processors and they are available on a large amount of distributed memory MIMD systems and even on shared memory MIMD systems for compatibility reasons. In addition there is a tendency to cluster shared memory systems, for instance by HIPPI channels, to obtain systems with a very high computational power. E.g., the Intel Paragon with the MP (Multi Processor) nodes, the NEC SX-4, and the Convex Exemplar SPP-2000X have this structure. In addition, the latter system has a software environment that allows virtual shared memory addressing.

# 2.2 Shared-memory SIMD machines

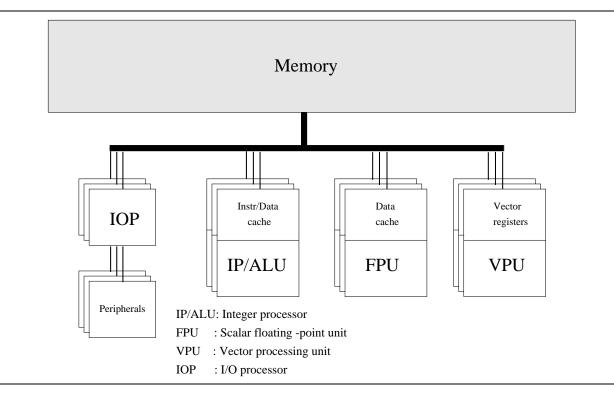

This subclass of machines is practically equivalent to the single-processor vector processors, although other interesting machines in this subclass have existed (viz., VLIW machines [16]). In the block diagram in Figure 1 we depict a generic model of a vector architecture. The single-processor vector machine will have only one of the VPUs depicted and the system may even have its scalar floating-point capability shared with the vector processor (as is the case in Cray systems). It may be noted that the VPU does not show a cache. Vectorprocessors do not employ a cache anymore. In many cases the vector unit cannot take advantage of it and execution speed may even be unfavourably affected because of frequent cache overflow.

Although vector processors have existed that loaded their operands directly from memory and stored the results again immediately in memory (CDC Cyber 205, ETA-10), all present-day vector processors use vector registers. This usually does not lower the speed of operations while providing much more flexibility in

Figure 1: Block diagram of a vector processor.

gathering operands and manipulation with intermediate results.

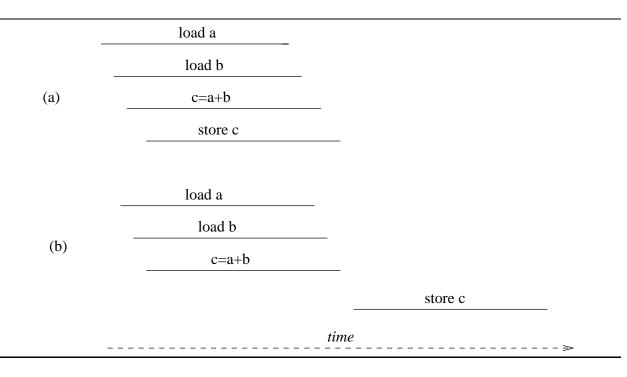

Because of the generic nature of Fig. 1 no details of the interconnection between the VPU and the memory are shown. Still, these details are very important for the effective speed of a vector operation: when the bandwidth between memory and the VPU is too small it is not possible to take full advantage of the VPU because it has to wait for operands and/or has to wait before it can store results. When the ratio of arithmetic to load/store operations is not high enough to compensate for such situations, severe performance losses may be incurred. The influence of the number of load/store paths for the dyadic vector operation c = a + b (a, b, and c vectors) is depicted in Figure 2. Because of the high costs of implementing these data paths between memory and the VPU, often compromises are sought and the number of systems that have the full required bandwidth (i.e., two load operations and one store operation at the same time) is limited.

The VPUs are shown as single blocks in Fig. 1. Yet, again there is a considerable diversity in the structure of VPUs. Every VPU consists of a number of vector functional units, or "pipes" that fulfill one or several functions in the VPU. Every VPU will have pipes that are designated to perform memory access functions, thus assuring the timely delivery of operands to the arithmetic pipes and of storing the results in memory again. Usually there will be several arithmetic functional units for integer/logical arithmetic, for floating-point addition, for multiplication and sometimes a combination of both, a so-called compound operation. Division is performed by an iterative procedure, table look-up, or a combination of both using the add and multiply pipe. In addition, there will almost always be a mask pipe to enable operation on a selected subset of elements in a vector of operands. Lastly, such sets of vector pipes can be replicated within one VPU (2-and 4-fold replication are common). Ideally, this will increase the performance per VPU by the same factor provided the bandwidth to memory is adequate.

# 2.3 Distributed-memory SIMD machines

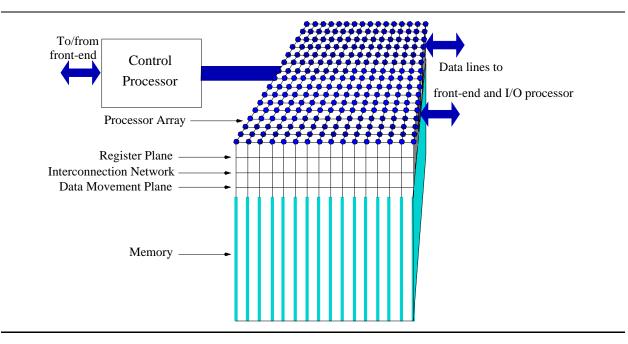

Machines of this type are sometimes also known as *processor-array* machines [9]. Because the processors of these machines operate in lock-step, i.e., all processors execute the same instruction at the same time (but on different data items), no synchronisation between processors is required. This greatly simplifies the

Figure 2: Schematic diagram of a vector addition. Case (a) when two load- and one store pipe are available; case (b) when two load/store pipes are available.

design of such systems. A *control processor* issues the instructions that are to be executed by the processors in the processor array. All currently available DM-SIMD machines use a front-end processor to which they are connected by a data path to the control processor. Operations that cannot be executed by the processor array or by the control processor are off-loaded to the front-end system. For instance, I/O may be through the front-end system, by the processor array machine itself or both. Figure 3 shows a generic model of a DM-SIMD machine of which actual models will deviate to some degree. Figure 3 might suggest that all processors in such systems are connected in a 2-D grid and indeed, the interconnection topology of this type of machines always includes the 2-D grid. As opposing ends of each grid line are also always connected the topology is rather that of a torus. For several machines this is not the only interconnection scheme: They might also be connected in 3-D, diagonally, or more complex structures.

It is possible to exclude processors in the array from executing an instruction on certain logical conditions, but this means that for the time of this instruction these processors are idle (a direct consequence of the SIMD type operation) which immediately lowers the performance. Another factor that may adversely affect the speed occurs when data required by processor i resides in the memory of processor j (in fact, as this occurs for all processors at the same time this effectively means that data will have to be permuted across the processors). To access the data in processor j, the data will have to be fetched by this processor and then send through the routing network to processor i. This may be fairly time consuming. For both reasons mentioned DM-SIMD machines are rather specialised in their use when one wants to employ their full parallelism. They perform excellently on many digital signal and image processing applications. They also are well suited for certain types of Monte Carlo simulations. In general, when virtually no data exchange between processors is required and the same type of operations is done on massive datasets, these machines can be very effective.

The control processor as shown in Figure 3 may be more or less intelligent. It issues the instruction sequence that will be executed by the processor array. In the worst case (that means a less autonomous control processor) when an instruction cannot be executed on the processor array (e.g., a simple print instruction) it might be off-loaded to the front-end processor which may be much slower than execution on the control processor. In case of a more autonomous control processor, this can be avoided thus saving processing interrupts both on the front-end and the control processor. Most DM-SIMD systems have the possibility to

Figure 3: A generic block diagram of a distributed memory SIMD machine.

handle I/O independently from the front-end processors. This is not only favourable because the communication between the front-end system and processor-array machine is avoided. The (specialised) I/O devices for the processor-array system are generally much more efficient in providing the necessary data directly to the memory of the processor array. Especially for very data-intensive applications like radar and image processing such I/O systems are very important.

A feature that is peculiar to this type of machines is that the processors sometimes are of a very simple bit-serial type, i.e., the processors operate on the data items bitwise, irrespective of their type. So, e.g., operations on integers are produced by software routines on these simple bit-serial processors which takes at least as many cycles as the operands are long. So, a 32-bit integer result will be produced two times faster than a 64-bit result. For floating-point operations a similar situation holds, be it that the number of cycles required is a multiple of that needed for an integer operation. As the number of processors in this type of systems is mostly large (1024 or larger, the Alenia Quadrics is a notable exception, however), the slower operation on floating-point numbers can be often compensated for by their number, while the cost per processors are added to the processor-array. Their number is 8–16 times lower than that of the bit-serial processors because of the cost argument. An advantage of bit-serial processors is that they may operate on operands of any length. This is particularly advantageous for random number generation (which often boils down to logical manipulation of bits) and for signal processing because in both cases operands of only 1–8 bits are abundant. As the execution time for bit-serial machines is proportional to the length of the operands, this may result in significant speedups.

# 2.4 Shared-memory MIMD machines

Figure 1 shows one subclass of this type of machines, viz., the multi-processor vector processor. The figure shows that more than one FPU and/or VPU may be possible in one system.

The main problem one is confronted with in shared-memory systems is that of the connection of the CPUs to each other and to the memory. As more CPUs are added, the collective bandwidth to the memory ideally should increase linearly with the number of processors, while each processor should preferably communicate directly with all others without the much slower alternative of going via the memory. Unfortunately, full interconnection is quite costly, growing with  $O(n^2)$  while increasing the number of processors with O(n). So,

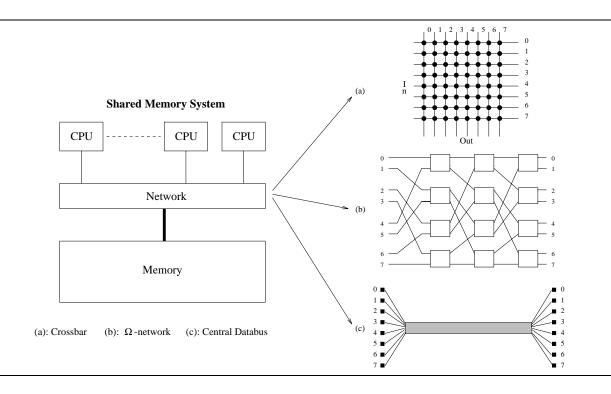

various alternatives have been tried. Figure 4 shows some of the interconnection structures that are (and have been) used.

As can be seen from the figure, a crossbar uses  $n^2$  connections, an  $\Omega$ -network uses  $n \log_2 n$  connections while, with the central bus, there is only one connection. This is reflected in the use of each connection path for the different types of interconnections: for a crossbar each datapath is direct and does not have to be shared with other elements. In case of the  $\Omega$ -network there are  $\log_2 n$  switching stages and as many data items may have to compete for any path. For the central databus all data have to share the same bus, so n data items may compete at any time.

The bus connection is the least expensive solution, but it has the obvious drawback that bus contention

Figure 4: Some examples of interconnection structures used in shared-memory MIMD systems.

may occur thus slowing down the computations. Various intricate strategies have been devised using caches associated with the CPUs to minimise the bus traffic. This leads however to a more complicated bus structure which raises the costs. In practice it has proved to be very hard to design buses that are fast enough, especially since the speed of the processors is still increasing very quickly. It imposes an upper bound on the number of processors that can be connected by a bus. This number appears in practice not to exceed 10–20. In 1992, a new standard (IEEE P896) for a fast bus has been defined. The bus may connect either components within a system or systems with each other. This bus, called the Scalable Coherent Interface (SCI) should provide a point-to-point bandwidth of 200–1,000 Mbyte/s. It is in fact used in the HP/Convex SPP-2000, but could also be used within a network of workstations. The SCI is much more than a simple bus and it can act as the physical network layer for distributed computing, see [12].

The  $\Omega$ -network is a structure which is situated somewhere in between a bus and a crossbar which respect to potential capacity and costs. At this moment commercially available machines like the IBM SP2, the Meiko CS-2, and the NEC Cenju-3 use this network structure, but a number of experimental machines also have used the same or a similar kind of interconnection. The BBN TC2000, that behaved like a virtual shared-memory MIMD system, used an analogous type of network (a Butterfly-network) and it is quite conceivable that new machines may use it, especially as the number of processors grows. For a large number of processors the  $n \log_2 n$  connections become quickly more attractive than the  $n^2$  used in crossbars. Of course, the switches at the intermediate levels should be sufficiently fast to cope with the bandwidth required. Obviously, not

only the *structure* but also the *width* of the links between the processors is important: a network using 16-bit parallel links will have a bandwidth which is 16 times higher than a network with the same topology implemented with serial links.

In all present-day multi-processor vectorprocessors crossbars are used. This is still feasible because the maximum number of processors in a system is still rather small (32 at most presently). When the number of processors would increase, however, technological problems might arise. Not only it becomes harder to build a crossbar of sufficient bandwidth for the larger numbers of processors, the processors themselves generally also increase in speed individually, doubling the problems of making the bandwidth of the crossbar match that of the bandwidth required by the processors.

Whichever network is used, any type of processor (scalar or vector) in principle could be employed for any topology. In practice, however, bus structured machines do not employ vectorprocessors as the bandwidths of these would grossly mismatch with any bus that could be constructed at reasonable costs. All available bus-oriented systems use RISC processors. The local caches of the processors can sometimes alleviate the bandwidth problem if the data access can be satisfied by the caches thus avoiding references to the memory.

The systems discussed in this subsection are of the MIMD type and therefore different tasks may run on different processors simultaneously. In many cases synchronisation between tasks is required and again the interconnection structure is here very important. Most vectorprocessors employ special communication registers within the CPUs by which they can communicate directly with the other CPUs they have to synchronise with. A minority of systems synchronise via the shared memory. Generally, this is much slower but it may still be acceptable when the synchronisation occurs relatively seldom. Of course in bus-based systems synchronisation also has to be done via a bus. To assure a maximum speed for the synchronisation often a separate bus is employed to this end.

# 2.5 Distributed-memory MIMD machines

The class of DM-MIMD machines is undoubtly the fastest growing part in the family of high-performance computers. This type of machines is more difficult to deal with than shared-memory machines and DM-SIMD machines. The latter type of machines are processor-array systems in which the data structures that are candidates for parallelisation are vectors and multi-dimensional arrays that are laid out automatically on the processor array by the system software. For shared-memory systems the data distribution is completely transparant to the user. This is quite different for DM-MIMD systems where the user has to distribute the data over the processors and also the data exchange between processors has to be performed explicitly. The initial reluctance to use DM-MIMD machines seems to have been decreased. Partly this is due to the now existing standard software for communication ([7, 15]) and partly because, at least theoretically, this class of systems is able to outperform all other types of machines.

The advantages of DM-MIMD systems are clear: the bandwidth problem between CPU and memory that haunts shared-memory systems is avoided because the bandwidth scales up automatically with the number of processors. Furthermore, the speed of the memory which is another critical issue with shared-memory systems (to get a peak performance that is comparable to that of DM-MIMD systems, the processors of the shared-memory machines should be very fast and the speed of the memory should match it) is less important for the DM-MIMD machines, because more processors can be configured without the afore mentioned bandwidth problems.

Of course, DM-MIMD systems also have their disadvantages: The communication between processors is much slower than in SM-MIMD systems (typically 100–1000 times), and so, the synchronisation overhead in case of communicating tasks is generally orders of magnitude higher than in shared-memory machines. Moreover, data that is not residing in the local memory belonging to a particular processor has to be obtained from non-local memory (or memories). This is again on most systems a very slow process as compared to local data access. When the structure of a problem dictates a frequent exchange of data between processors and/or requires many processor synchronisations, it may well be that only a very small fraction of the theoretical peak speed can be obtained. As already mentioned, the data- and task decomposition are factors that mostly have to be dealt with explicitly, which may be far from trivial.

It will be clear from the paragraph above that also for DM-MIMD machines both the topology and the

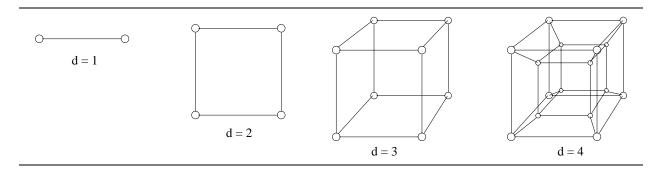

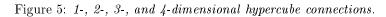

bandwidth of the data paths are of crucial importance for the practical usefulness of a system. Again, as in section 2.4, the richness<sup>1</sup> of the interconnection structure has to be balanced against the costs. Of the many conceivable interconnection structures only a few are used in practice. One of these is the so-called hypercube topology as depicted in Figure 5.

A nice feature of the hypercube topology is that for a hypercube with  $2^d$  nodes the number of communication steps to be taken between any two nodes is at most d. So, the dimension of the network grows only logarithmically with the number of nodes. In addition, theoretically, it is possible to simulate any other topology on a hypercube: trees, rings, complete and incomplete 2-D and 3-D meshes, etc. In practice, the exact topology for hypercubes does not matter too much because all systems in the market today employ what is called "wormhole routing". This means that when node i wants to communicate with node j a header message is sent from i to j resulting in a direct connection between these nodes. This is called a virtual channel or connection. As soon as this connection is established, the data proper is sent through this connection without disturbing the operation of the intermediate nodes. Except for a small amount of time in setting up the connection between nodes, the communication time has become virtually independent of the distance between the nodes. Of course, when several messages in a busy network have to compete for the same paths, waiting times are incurred as in any network that does not directly connect any processor to all others and often rerouting strategies are employed to circumvent busy links.

Many of the newly introduced massively parallel DM-MIMD systems seem to favour a 2- or 3-D mesh (torus) structure. The rationale for this seems to be that many simulations of large-scale physical phenomena can be mapped efficiently on this topology and that a richer interconnection structure hardly pays off. However, some systems maintain (an) additional network(s) besides the mesh to handle certain bottlenecks in data distribution and retrieval [10].

A large fraction of systems in the DM-MIMD class employs crossbars. For relatively small amounts of processors (in the order of 64) this may be a direct or 1-stage crossbar. To connect larger numbers of nodes multi-stage crossbars are used, i.e., the connections of a crossbar at level 1 connect to a crossbar at level 2, etc., instead of directly to nodes at more remote distances in the topology. In this way it is possible to connect in the order of a few thousands of nodes through only a few switching stages. Butterfly-,  $\Omega$ -, or shuffle-exchange networks are often employed in such systems.

As with SM-MIMD machines, a node may in principle contain any type of processor (scalar or vector) for computation or transaction processing together with local memory (with or without cache) and, in almost all cases, a separate communication processor with links to connect the node to its neighbours. Nowadays, the node processors are mostly off-the-shelf RISC processors sometimes enhanced by vector processors. A problem that is peculiar to this DM-MIMD systems is the mismatch of communication vs. computation speed that may occur when the node processors are upgraded, without also speeding up the intercommunication. In many cases this may result in turning computational-bound problems into communication-bound problems.

$<sup>^{1}</sup>$ By the "richness" of the interconnection structure we mean the number of links that connects each node to its neighbours. So, in a 2-D grid the interconnection is less rich than in a crossbar where any processor is a neighbour to all others.

# 3 Recount of the (almost) available systems

In this section we give a recount of all types of systems as discussed in the former section. When of a certain system various models are available, we will discuss them all at once. So, for instance, we will discuss Convex systems under one entry, SM-MIMD systems, even if a one-processor model of such a system strictly should be discussed under the SM-SIMD heading. We rather regard such systems a special cases of a general product line.

# 3.1 Shared-memory SIMD systems

In this class only one system is still actively marketed demonstrating the fact that this type of machines is only interesting for a rather small (but not unimportant) group of customers that have to do high-speed production work with well vectorised codes.

# 3.1.1 The Hitachi S3600 series.

Machine type: Vectorprocessor.

Models: S3600/120, S3600/140, S3600/160, S3600/180.

Operating system: VOS3/HAP/ES (IBM MVS compatible) and OSF/1.

Compilers: FORT77/HAP vectorising Fortran 77.

# System parameters:

| ${f Model}$             | S3600/120           | S3600/140             | S3600/160             | S3600/180           |

|-------------------------|---------------------|-----------------------|-----------------------|---------------------|

| Clock cycle VPU         | 4  ns               | 4  ns                 | 4  ns                 | 4  ns               |

| Clock cycle scal. proc. | 8  ns               | $8  \mathrm{ns}$      | $8  \mathrm{ns}$      | 8  ns               |

| Theor. peak performance | $0.25~{ m Gflop/s}$ | $0.5~{ m Gflop/s}$    | $1.0~{ m Gflop/s}$    | $2~{ m Gflop/s}$    |

| Main memory             | 128256MB            | $256-512 \mathrm{MB}$ | $256-512 \mathrm{MB}$ | 5121024MB           |

| Extended memory         | $\leq 6$ GB         | $\leq 16 \text{GB}$   | $\leq 16 \text{GB}$   | $\leq 16 \text{GB}$ |

#### Remarks:

The speed differences between the different models stem from replication of the multiply/add pipe in the models S3600/120–180. The /160 and /180 models have respectively two- and four-fold sets of a separate add- and a multifunctional multiply/add vector pipes. This should lead to a maximum of 3 results per clock cycle per pipe set. So, contrary to the information given by the vendor, the maximum performance of, e.g., the /180 should in some situations be 3 Gflop/s instead of 2.

Note that the clock cycle of the scalar processor is twice that of the VPU. The memory bandwidth from the memory from/to the CPU is 2 operands per clock cycle via 1 load and 1 load/store pipe per arithmetic pipe set, which is somewhat less than optimal. It is not possible to load two operands and store one result in one cycle. The /120 model lacks a separate load pipe, only a load/store pipe is present.

A unique feature of the S3600, as in its direct predecessor the S-820, is that all machines of the series are air cooled. All other machines in this class relied at least on water cooling.

Unlike the S-820 series, the S3600 series is also marketed worldwide, not only in Japan. This is also the case for the S3800 SM-MIMD machines 3.3.3.

# Measured performances:

In [4] a speed of 851 Mflop/s for the solution of a full linear system of order 1000 is reported for the S3600/160. The S3600/180 attains a performance of 1672 Mflop/s on the same problem.

#### 3.2.1 The Alenia Quadrics.

Machine type: Processor array. Models: Quadrics Qx, QHx, x = 1, 16. Front-end: Almost any Unix workstation.

**Operating system**: Internal OS transparent to the user, Unix on front-end

Connection structure: 3-D mesh, (see remarks).

**Compilers**: TAO: a Fortran 77 compiler with some Fortran 90 and some proprietary array extensions. **Vendors information Web page**: www.sede.enea.it/ hpcn/moshpce/quadr01e.html

# System parameters:

| Model                   | $\mathrm{Q}x$           | $\mathrm{QH}x$            |

|-------------------------|-------------------------|---------------------------|

| Clock cycle             | 40  ns                  | 40 ns                     |

| Theor. peak performance |                         |                           |

| Per Proc. (32-bits)     | $50 \mathrm{Mflop/s}$   | $50 \mathrm{Mflop/s}$     |

| Maximal $(32-bits)$     | $6.4  \mathrm{Gflop/s}$ | $100 \; \mathrm{Gflop/s}$ |

| Memory                  | $\leq 2 \text{ GB}$     | $\leq 32 \text{ GB}$      |

| No. of processors       | 8 - 128                 | 128 - 2048                |

| Communication bandwidth |                         |                           |

| Per Proc.               | 50  MB/s                | 50  MB/s                  |

| Aggregate local         | $\leq 6 \text{ GB/s}$   | $\leq 96 \text{ GB/s}$    |

| Aggregate non-local     | $\leq 1.5 \text{ GB/s}$ | $\leq 24 \text{ GB/s}$    |

#### Remarks:

The Quadrics is a commercial spin-off of the APE-100 project of the Italian National Institute for Nuclear Physics. Systems are available in multiples of 8 processor nodes in the Q-model where up to 16 boards can be fitted into one create or in multiples of 128 nodes in the QH-model by adding up to 15 crates to the minimal 1-crate system. The interconnection topology of the Quadrics is a 3-D grid with interconnections to the opposite sides (so, in effect a 3-D torus). The 8-node floating-point boards (FPBs) are plugged into the crate backplane which provides point-to-point communication and global control distribution. The FPBs are configured as  $2^3$  cubes that are connected to the other boards appropriately to arrive at the 3-D grid structure.

The basic floating-point processor, the so-called MAD chip, contains a register file of 128 registers. Of these registers the first two hold permanently the values 0 and 1 to be able to express any addition or multiplication as a "normal operation", i.e., a combined multiply-add operation, where an addition is of the form,  $a \times 1 + b$  and a multiplication is  $a \times b + 0$ . In favourable circumstances the processor can therefore deliver two floating-point operations per cycle. Instructions are centrally issued by the controller at a rate of one instruction every two clock cycles.

Communication is controlled by the Memory Controller and the Communication Controller which are both housed on the backplane of a crate. When the Memory Controller generates an address it is decoded by the Communication Controller. In case non-local access is desired, the Communication Controller will provide the necessary data transmission. The memory bandwidth per processor is 50 MB/s which means that every 2 cycles an operand can be shipped in or out a processor. The bandwidth for non-local communication turns out to be only four times smaller than local memory access.

The Quadrics communicates with the front-end system via a T805 transputer-based interface system, called the Local Asynchronous Interface (LAI). The interface can write and read the memories of the nodes and the Controller. Presently, the bandwidth of the interface to the front-end processor is not very large (1 MB/s). It is expected that this can be improved by about a factor of 30 in the near future. I/O has to be performed via the front-end system and will therefore be relatively slow.

The TAO language has several extensions to employ the SIMD features of the Quadrics. Firstly, floatingpoint variables are assumed to be local to the processor that owns them, while integer variables are assumed to be global. Local variables can be promoted to global variables. Other extensions are the ANY, ALL, and WHERE/END WHERE keywords that can be used for global testing and control. Processors that not meet a global condition effectively skip the operation(s) that are associated with it. For easy referencing nearest-neighbour locations special constants LEFT, RIGHT, UP, DOWN, FRONT, and BACK are provided. In addition, new data types and operators on these data types are supported together with overloading of operators. This enables very concise code for certain types of calculations.

#### Measured performances:

As yet, no performance figures are available for the Quadrics systems.

# 3.2.2 The Cambridge Parallel Processing Gamma II.

Machine type: Processor array.

Models: Gamma II 1000, Gamma II 4000.

Front-end: Sun of HP; stand-alone for dedicated applications.

**Operating system**: Internal OS transparent to the user, Unix on front-end

Connection structure: 2-D mesh, row- and column datapaths (see remarks).

**Compilers**: FORTRAN-PLUS (a Fortran 77 compiler with some Fortran 90 and some proprietary array extensions), C++.

Vendors information Web page: www.TechCentral.com.

#### System parameters:

| ${f Model}$             | Gamma II 1000        | Gamma II $4000$       |

|-------------------------|----------------------|-----------------------|

| Clock cycle             | $33 \mathrm{\ ns}$   | $33 \mathrm{\ ns}$    |

| No. of processors       | 1024                 | 4096                  |

| Theor. peak performance |                      |                       |

| Per Proc. (Mflop/s)     | 1.2                  | 1.2                   |

| 1-bit Gop/s             | 30.7                 | 122.8                 |

| 8-bit Gop/s             | 30.7                 | 122.8                 |

| Gflop/s (32-bit) total  | 1.2                  | 4.8                   |

| Program memory          | $\leq 4 \text{ MB}$  | $\leq 4 \text{ MB}$   |

| Data memory             | $\leq 32 \text{ MB}$ | $\leq 128 \text{ MB}$ |

| Int. comm. speed        |                      |                       |

| Across row, column      | 120  MB/s            | 480  MB/s             |

| Memory to PE            | $3.84~\mathrm{GB/s}$ | $15.4 \mathrm{~GB/s}$ |

#### Remarks:

In November 1995 the new Gamma II models has been announced by CPP. In essence there is not much difference with its predecessor the DAP Gamma. However, the clock cycle has tripled to 33 ns with an equivalent rise in the peak performance of the systems.

The Gamma II is presented as the fourth generation of this type of machine. Indeed, the macro architecture of the systems has hardly changed since the first ICL DAP (the first generation of this system) was conceived. As in the ICL DAP in the Gamma 1000 models the 1024 processors are ordered in a  $32 \times 32$  array, while the Gamma 4000 has 4096 processors arranged in a  $64 \times 64$  square.

The systems are able to operate byte parallel on appropriate operands to speed up floating-point operations, however, for logical operations bit-wise operations are possible, which makes the machines quite fast in this respect. As the byte parallel code consists of separate sequences of microcode instructions, the bit processor plane and the byte processor plane are in fact independent and can work in parallel. This is also the case for I/O operations. Also character-handling can be done very efficiently. This is the reason why Gamma systems are often used for full text searches.

As in all processor-array machines, the control processor (called the Master Control Unit (MCU) in the DAP) has a separate memory to hold program instructions while the data are held in the data memory associated with each Processing Element (PE) in the processor array. So, for a Gamma 1000 with 32 MB of data memory each PE has 32 KB of data memory directly associated to it. To access data in other PE's

memories these must be brought up to the data routing plane and shifted to the appropriate processor.

As already mentioned under the heading of the connection structure, there are two ways of connecting the PEs. One is the 2-D mesh that connects each element to its North-, East-, West-, and South neighbour. In addition there are row- and column data paths that enable the fast broadcast of a row or column to an entire matrix by replication. Conversely, they can be used for row- or column wise reduction of matrix objects into a column- or row vector of results from, e.g., a summing- or maximum operation.

Separate I/O processors and disk systems can be attached to the Gamma directly thus not burdening the front-end machine (and the connection between front-end and DAP) with I/O operations and unnecessary data transport. One of these I/O devices is the GIOC that can transport data to the data memory at a sustained rate of 80 MB/s transposing the data to the vertical storage mode of the data memory on the fly. Also, a direct video interface is available to operate a frame buffer.

A nice (non-standard) feature of the FORTRAN-PLUS compiler is the possibility to use logical matrices as indexing objects for computational matrix objects. This enables a very compact notation for conditional execution on the processor array. In addition, recently C++ is available.

#### Measured Performances:

In [5] the speed of matrix multiplication on various DAP models (precursors of the Gamma systems) is analyzed. The documentation states 32-bit floating-point add speed of 1.68 Gflop/s on 4096 PEs, while a 32-bit 1,024 complex FFT would attain 2.49 Gflop/s. No independent performance figures for the Gamma II systems are available.

#### 3.2.3 The MasPar MP-1.

Machine type: Processor array.

Models: MP1101, MP1102, MP1104, MP1208, MP1216.

Front-end: DECstation 5000 or DEC VAX.

**Operating system**: Internal OS transparent to the user, Ultrix or VMS on front-end.

Connection structure: 2-D mesh, crossbar (see remarks).

**Compilers**: MPL: (C with extensions), MPF: (Fortran 90-like with extensions).

#### System parameters:

| Model                   | MP1101    | MP1102    | MP1104               | MP1208                | MP1216            |

|-------------------------|-----------|-----------|----------------------|-----------------------|-------------------|

| Clock cycle             | 83  ns    | 83  ns    | 83  ns               | $83 \mathrm{~ns}$     | $83  \mathrm{ns}$ |

| No. of processors       | 1024      | 2048      | 4096                 | 8192                  | 16384             |

| Theor. peak performance |           |           |                      |                       |                   |

| Per proc. (Mflop/s)     | 0.034     | 0.034     | 0.034                | 0.034                 | 0.034             |

| Mop/s (32-bit)          | 1600      | 3200      | 6400                 | 13000                 | 26000             |

| Mop/s (64-bit)          | 800       | 1600      | 3200                 | 6400                  | 13000             |

| M flop/s (32-bit)       | 75        | 150       | 300                  | 600                   | 1200              |

| M flop/s (64-bit)       | 34        | 69        | 138                  | 275                   | 550               |

| Program memory          | 1-4MB     | 1-4MB     | 1-4MB                | 1-4MB                 | 1-4MB             |

| Data memory             | 16-64MB   | 32-128MB  | $64-256 \mathrm{MB}$ | $128-512 \mathrm{MB}$ | 256-1GB           |

| Int. comm. speed        |           |           |                      |                       |                   |

| Via Xnet (n. neighbour) | 1.4  GB/s | 2.8  GB/s | $5.7~\mathrm{GB/s}$  | 11.5  GB/s            | 23.0  GB/s        |

| Via global router       | 80  MB/s  | 160  MB/s | 320  MB/s            | 640  MB/s             | 1.28  GB/s        |

#### Remarks:

The Processing Elements (PEs) of the MP-1 are more intricate than those from the DAP Gamma II (3.2.2). Each PE contains a 4-bit parallel Arithmetic/Logic Unit together with a 1-bit functional unit, a 16-bit exponent unit and a 64-bit mantissa unit. These units may be operated separately or in concord (e.g., for floating-point calculations). Because of the hardware implementation of the PEs, only 1-, 8-, 16-, 32-, and 64-bit data types are allowed.

Unlike on the DAP Gamma II, on the MP-1 it is possible to address data items in the data memories indi-

rectly. This greatly facilitates manipulation of matrix objects indexed through an index matrix.

One type of interconnection of the PEs is a 2-D rectangular mesh (with wrap-around). This is however implemented by connecting the PEs diagonally via 3-way switches. As the setting of the switches only takes 1 cycle, this means that every PE can reach it 8 surrounding neighbours in 1 cycle. For more general routing schemes a Global Router is available. This acts, in principle, as a three-stage crossbar. PEs are arranged in clusters of  $4 \times 4$ , which connect to other clusters through the first level of the crossbar. All clusters connect via an intermediate stage to the target stage (again at cluster level). The ports from the clusters are multiplexed to the individual PEs within a cluster. As this type of communication is fairly intricate, it is much slower than via the Xnet (see system parameter list above). As with the DAP Gamma II, there are provisions for connecting a frame buffer and/or disks directly to the MP-1. Also like the DAP, the MP-1 is essentially a single-user machine, that is, only one user at a time can have a task on the MP-1. Of course, tasks can be scheduled via a multi-user interface on the front-end system.

The MP-1 features a very nice X-window based programming environment, MPPE, which integrates an interactive source debugger, a profiler, and output windows in one environment.

#### Measured Performances:

In [4] the solution of a full linear system was reported on a 16384 PE machine with a speed of 440 Mflop/s. The same report estimated the peak performance to be 580 Mflop/s in 64-bit precision.

#### 3.2.4 The MasPar MP-2.

Machine type: Processor array.

Models: MP2201, MP2202, MP2204, MP2208, MP2216.

Front-end: DECstation 5000 or DEC VAX.

Operating system: Internal OS transparent to the user, Ultrix or VMS on front-end.

Connection structure: 2-D mesh, crossbar (see remarks).

Compilers: MPL: (C with extensions), MPF: (Fortran 90-like with extensions).

#### System parameters:

| Model                   | MP2201               | MP2202            | MP2204            | MP2208            | MP2216          |

|-------------------------|----------------------|-------------------|-------------------|-------------------|-----------------|

| Clock cycle             | 80  ns               | 80  ns            | 80  ns            | 80  ns            | 80  ns          |

| No. of processors       | 1024                 | 2048              | 4096              | 8192              | 16384           |

| Theor. peak performance |                      |                   |                   |                   |                 |

| Per proc. (Mflop/s)     | 0.15                 | 0.15              | 0.15              | 0.15              | 0.15            |

| Mop/s (32-bit)          | 4250                 | 8500              | 17000             | 34000             | 68000           |

| Mop/s (64-bit)          | 2100                 | 4250              | 8500              | 17000             | 34000           |

| Mflop/s (32-bit)        | 400                  | 800               | 1600              | 3200              | 6300            |

| M flop/s (64-bit)       | 150                  | 300               | 600               | 1200              | 2400            |

| Program memory          | 1-4MB                | 1-4MB             | 1-4MB             | 1-4MB             | 1-4MB           |

| Data memory             | $64 \mathrm{MB}$     | $128 \mathrm{MB}$ | $256 \mathrm{MB}$ | $512 \mathrm{MB}$ | $1 \mathrm{GB}$ |

| Int. comm. speed        |                      |                   |                   |                   |                 |

| Via Xnet (n. neighbour) | $1.25~\mathrm{GB/s}$ | 2.5  GB/s         | 5.0  GB/s         | 10.0  GB/s        | 20.0  GB/s      |

| Via global router       | 80  MB/s             | 160  MB/s         | 320  MB/s         | 640  MB/s         | 1.28  GB/s      |

#### Remarks:

Apart from being roughly 2.5 times faster than the MasPar MP-1 (3.2.4), there is little difference between the MP-2 and the MP-1. The gain in speed relative to the MP-1 is accomplished by using a processor with a higher degree of bit-parallelism. This resulted in a higher performance at the expense of the number of data formats: only 32-bit and 64-bit data are allowed on the MP-2.

MasPar will market both the MP-1 and MP-2. In the view of the company there is a market for both. With a fixed budget one can make a choice for a system with larger memory, but slower or a faster system with a smaller memory. Software and tools are exactly the same for both types of machines.

#### Measured Performances:

[4] reports a speed of 1.6 Gflop/s to solve a 11,264 order linear system on 16,384 processors.

# 3.3 Shared-memory MIMD systems

For some systems in this category it will not always be possible to discuss all models of a particular product line because the number of configurations is simply too large. However, we attempt to give the representative configurations for such systems. In addition, when single-processor versions of a certain machine are available, this is regarded as a special case of a multi-processor version and the one-processor versions are omitted from section 3.2 where they could have been treated.

Furthermore, we have included systems here that have a shared-memory model as a basis but that may be extended by coupling several of these systems together in a distributed memory way. The distinction is not always very clear when looking at the end product: a multi-frame DEC AlhpaServer (3.3.2) and an HP/Convex SPP-2000(3.4.8) look very much alike. The difference lies in the integration. In the latter machine the distributed memory extension of multi-CPU nodes was a basis for the architecture while in the former DEC system it is more like an added feature.

# 3.3.1 The Cray Research Inc. Cray J90-series, T90 series.

Machine type: Shared-memory multi-vectorprocessor.

Models: Cray J90, T90.

Operating system: UNICOS (Cray Unix variant).

Compilers: Fortran, C, C++, Pascal, ADA.

Vendor information Web page: www.cray.com.

# System parameters:

| Model                   | Cray J90                  | Cray T90                  |

|-------------------------|---------------------------|---------------------------|

| Clock cycle             | $10  \mathrm{ns}$         | $2.2  \mathrm{ns}$        |

| Theor. peak performance |                           |                           |

| Per processor           | $200 { m Mflop/s}$        | $1.8 \; \mathrm{Gflop/s}$ |

| Maximal                 | $6.4 \; \mathrm{Gflop/s}$ | $58 G \mathrm{flop/s}$    |

| Main memory             | $\leq 4 \text{ GB}$       | $\leq 8 \text{ GB}$       |

| Memory bandwidth        |                           |                           |

| Single proc. bandwidth  | $1.6~\mathrm{GB/s}$       | $24~\mathrm{GB/s}$        |

| No. of processors       | 4 - 32                    | 1 - 32                    |

# Remarks:

Cray Research Inc. (CRI) has recently been taken over by Silicon Graphics (SGI) but for the next few years Cray will maintain separate product lines from SGI. Here we discuss the Cray-inherited vector systems.

Cray supports at this moment 3 product lines (apart from the SuperSparc-based CS6400 which is targeted to the commercial market and is not discussed in this report). Two of these are multi-headed vector processors which are discussed here. The third is the T3E, a DM-MIMD machine that will be described in section 3.4.4.

The Cray J90 series is the entry level model announced in September 1994. The J90 series is based on CMOS technology which has a low power consumption (all J90s are air cooled) and low production costs. The machine is binary compatible with the high-end systems. It has one multiply and add vector pipe set per CPU at a clock cycle of 10 ns which results in a theoretical peak performance of 200 Mflop/s. Furthermore, a cache has been added to speed up scalar processing (as in the Convex C4 series, see 3.3.4). It is interesting to note that the strategy of using more (four) multi-functional pipes as in the predecessor, the Y-MP EL has been left again to return to the classic two-pipe/CPU design.

The Cray T90 series is built in ECL logic and has therefore a much lower clock cycle (2.2 ns) and correspondingly faster SRAM memory. As its direct predecessor, the Cray C90, every CPU contains two vector add and multiply pipes. This gives rise to a maximum of 4 floating-point results/clock cycle/CPU equivalent to a theoretical peak performance of 1.8 Gflop/s per CPU or 58 Gflop/s for a maximal system.

The Cray T90 machines are at this moment the only ones with a memory bandwidth as seems optimal for vector processors: two operands can be loaded and one result can be stored in one cycle for each pipe set. For the T90 this meant that the relative bandwidth has to be 48 bytes/cycle/CPU. This has indeed been

accomplished and observed results indicate that for the T90 the performance scales up with the clock cycle and the number of functional units (see measured performances below). For the J90 series the bandwidth is lower: 16 bytes/cycle. This is regrettably less than was available in its predecessors, the Y-MP EL machines, and it might adversely affect the efficiency.

Another property that is unique for the Cray T90 systems is that they do not have a separate scalar processor but that scalar- and vector code have to share the same functional units. However, a small scalar cache is added to speed up scalar calculations. The Cray J90 series has separate scalar processors. Theoretically, the absence of separate scalar processors might impair the throughput speed (Hitachi (3.3.3) even adds an extra scalar processor in the S-3800 series to combat excessive context switching). However, in practice the drawbacks seem rather limited.

Contrary to earlier high-end Cray systems, the T90 now features compatibility with the IEEE 754 floatingpoint standard. Formerly, Cray-specific floating-point arithmetic was employed which could give rise to problems in data exchange with other systems and in different computational results due to the difference in arithmetic.

# Measured Performances:

On the T90 in [4] a speed of 29.4 Gflop/s was found on a 32 processor machine for the solution of an order 1000 dense linear system. For a J90 series machine with 32 processors a speed of 4.486 Gflop/s was observed for the same problem, which amounts to efficiencies of 51 and 70% for the T90 and the J90, respectively.

#### 3.3.2 The Digital Equipment Corp. AlphaServer.

Machine type: RISC-based distributed-memory multi-processor.

Models: AlphaServer 8200 5/440, 8400 5/440, 8400 Cluster.

Operating system: Digital Unix (DEC's flavour of Unix).

Connection structure: Crossbar (see remarks).

Compilers: Fortran 77, HPF, C, C++.

Vendors information Web page: www.digital.com:80/info/hpc.

#### System parameters:

| Model                                                             | 8200/440                    | 8400/440                    | Cluster                                    |

|-------------------------------------------------------------------|-----------------------------|-----------------------------|--------------------------------------------|

| Clock cycle                                                       | $2.3 \mathrm{ns}$           | $2.3 \mathrm{ns}$           | $2.3 \mathrm{ns}$                          |

| Theor. peak performance<br>Per proc. (64-bit)<br>Maximal (64-bit) | 875 Mflop/s<br>5.25 Gflop/s | 875 Mflop/s<br>10.5 Gflop/s | 875 Mflop/s<br>84 Mflop/s                  |

| Main memory                                                       | $\leq 6 \text{ GB}$         | $\leq 14 \text{ GB}$        | $\leq 36 \text{ GB}$                       |

| Memory bandwidth<br>Processor/memory<br>Between cluster nodes     | 1.6 GB/s                    | 1.6 GB/s                    | $1.6~\mathrm{GB/s}$<br>$100~\mathrm{MB/s}$ |

| No. of processors                                                 | 6                           | 12                          | 96                                         |

#### Remarks:

The AlphaServers are symmetric multi-processing systems which are based on the Alpha 21164A processor. The 8200 model is a somewhat smaller copy of the 8400 model: in the 8200 a maximum of 6 CPUs can be accomodated while this number is 12 for the 8400 model. Also, there is room for at most 6 GB of memory in the 8200 while the 8400 can house 14 GB. However, the amount of CPUs and memory is not independent. For instance, the 8400 has 9 system slots. One of these is reserved for I/O and one will have to contain at least one CPU module which can contain 1 or 2 CPUs. From the remaining slots 6 can be used either for memory or for a CPU module. So, one has to choose for either higher computational power or for more memory. This can potentially be a problem for large applications that require both.

AlphaServers can be clustered using PCI-Memory Channel link cables that are connected to a hub. The systems need not be of the same model. The bandwidth of this interconnect is slightly over 100 MB/s. Up to eight systems can be coupled in this way. To support this kind of cluster computing, HPF and optimised versions of PVM and MPI are available.

# Measured Performances:

As yet, only single system results for the AlphaServer 8400 are available. No cluster results are known. In [4] a speed of 6.7 Gflop/s for an 12-processor system are reported for the solution of a dense linear system of order 9548.

# 3.3.3 The Hitachi S3800 series.

Machine type: Vector processor.

**Models**: S3800/x60, S3800/y8z; x = 1, 2 y = 1, 2, 4 z = 0, 2. **Operating system**: VOS3/HAP/ES (IBM MVS compatible) and OSF/1. **Compilers**: FORT77/HAP vectorising Fortran 77.

System parameters:

| Model                   | S3800/x60                | S3800/y8z           |

|-------------------------|--------------------------|---------------------|

| Clock cycle VPU         | $2  \mathrm{ns}$         | 2  ns               |

| Clock cycle scal. proc. | 6  ns                    | 6  ns               |

| Theor. peak performance | 4-8 Gflop/s              | 8-32 Gflop/s        |

| No. of processors       |                          |                     |

| Scalar                  | 1 - 2                    | 1 - 4               |

| Vector                  | 1 - 2                    | 1 - 4               |

| Main memory             | $256 - 1024 \mathrm{MB}$ | 512-2048MB          |

| Extended memory         | $\leq 16 \text{GB}$      | $\leq 32 \text{GB}$ |

# Remarks:

The S3800 is the current top-end system of Hitachi's S-3000 series. Five different models are offered: The 160 and the 260 in which the 260 is simply the 2-CPU version of the 160. Furthermore, there is a sub-series 180, 280, and 480, of which the 280 and 480 are again 2-CPU and 4-CPU versions of the 180. However, in addition, there is a model 182 with 2 scalar processors and 1 vector processor as is offered in the former Fujitsu VPX200 series and for the same reason: context switching delay between jobs should be reduced by this scheme. The smallest model, the S-3800/160 has 4 multi-functional multiply/add pipes which may deliver up to 8 results per clock cycle. This is equivalent to 4 Gflop/s. In the /180 the number of pipes is doubled to 8 with a corresponding peak performance of 8 Gflop/s. All models feature one or more separate divide pipes. As the multi-headed systems can work in parallel, the top model, the S-3800/480, may theoretically attain a speed of 32 Gflop/s.

Hitachi now delivers an auto-parallelising compiler, which features parallelising compiler directives similar to those of Cray and NEC. The OSF/1 system can be run under the MVS-like VOS3/HAP/ES, but it can also be run as a native operating system.

# Measured Performances:

The first S3000 system, a S3800/480, was installed in January 1993 at the University of Tokyo. Tests with the EuroBen benchmark were done on this system in July-September 1993. During these tests a speed of 5.7 Gflop/s was observed for the evaluation of a 9<sup>th</sup> degree polynomial on a single processor. In matrix-vector multiplication, speeds of 6.5 Gflop/s on one processor were measured (see [17, 18]). In [4] a speed of 28.4 Gflop/s on 4 processors is reported for the solution of an order 15,500 dense linear system. The efficiency is here 89%.

# 3.3.4 The HP/Convex C4600 series.

Machine type: Shared-memory multi-vectorprocessor.

Models: C46x0, x = 1,...,4

Operating system: ConvexOS (Convex's Unix variant).

Compilers: Fortran, C, C++, ADA, Lisp.

Vendors Information Web page: www.convex.com/prod\_serv/prod\_serv.html.

### System parameters:

| Model                             | C4600                     |

|-----------------------------------|---------------------------|

| Clock cycle                       | $7.41  \mathrm{ns}$       |

| Theor. peak performance           |                           |

| Per proc. (64-bit prec.)          | 810  Mflop/s              |

| Per proc. $(32\text{-bit prec.})$ | $1620 { m Mflop/s}$       |

| Maximal, 64-bit precision         | 3240  Mflop/s             |

| Maximal, 32-bit precision         | $6480 \ \mathrm{Mflop/s}$ |

| No. of processors                 | 1 - 4                     |

| Main memory                       | $\leq 4GB$                |

| Memory bandwidth                  |                           |

| Single proc. bandwidth            | $1080 \ \mathrm{MB/s}$    |

#### Remarks:

In November 1995 Convex Computer Corp. has become a subsidiary of Hewlett Packard. This has, at least for the moment no impact on the products that are marketed by HP/Convex. Both the vectorprocessors and the Exemplar SPP series (see section 3.4) will stay on the market. The C4600 series is the fourth generation of vectorprocessors from Convex. Unlike in the former C3800 series, with a maximum of 8 processors, the highest number of processors is four in the C4640 model. A major difference with the former generations is that more functional unit sets per CPU are present: six general purpose functional units. This brings the number of floating-point results per cycle to 6 in the ideal case. Because the floating-point units are general the opportunities for linking or independent processing are increased with respect to specialised multiply and add pipes which increases the scheduling density of operations. In addition, some logical operations can be done in the functional units which enables 32-bit convolutions to be done in excess of 1 Gflop/s (this is called the "extended architecture" in Convex jargon).

As in the former C3400 and C3800 GaAs components are used to arrive at the cycle time of 7.41 ns. Also like in these former models, there is difference in speed of a factor of two between single precision (32 bits) and double precision (64 bits) calculations.

As for the Convex Exemplar SPP-2000 (see 3.4.8) an "application compiler" is available that is capable of interprocedural analysis. This can greatly enhance the vectorisability of some codes and in general is beneficial in optimising large codes.